# A Design Procedure for All-Digital Phase-Locked Loops Based on a Charge-Pump Phase-Locked-Loop Analogy

Volodymyr Kratyuk, Student Member, IEEE, Pavan Kumar Hanumolu, Member, IEEE, Un-Ku Moon, Senior Member, IEEE, and Kartikeya Mayaram, Fellow, IEEE

Abstract-In this brief, a systematic design procedure for a second-order all-digital phase-locked loop (PLL) is proposed. The design procedure is based on the analogy between a type-II second-order analog PLL and an all-digital PLL. The all-digital PLL design inherits the frequency response and stability characteristics of the analog prototype PLL.

Index Terms-All-digital phase-locked loop (PLL), bilinear transform, digital loop filter, digitally controlled oscillator.

#### I. INTRODUCTION

**R** ECENT advances in integrated circuit (IC) technology make fabrication processes make fabrication processes very suitable for digital designs. Small-area and low-voltage designs are mandated by market requirements. Another advantage of a digital design is its scalability and easy redesign with process changes or shrinks. Since analog blocks are present in a number of digital and mixed-signal ICs, their redesign is an important factor in the release of a new product. However, the performance requirements of analog blocks necessitates a complete redesign in a new process, thereby increasing the design cycle time. Reducing the amount of analog circuitry can improve the redesign of these mixed-signal ICs.

Recently, several digital and all-digital phase-locked loops (PLLs) for different applications (including multigigahertz ones) have been reported [1]–[4]. They demonstrate the ability of a digital implementation to achieve the performance of analog PLLs and even outperform them. There are several other advantages of a digital implementation of PLLs. These include eliminating the noise-susceptible analog control for a voltage-controlled oscillator (VCO) and the inherent noise immunity of digital circuits.

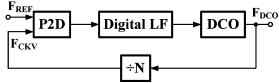

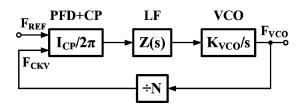

Analog PLLs (Fig. 1) have been investigated for the past several decades. As a result, different types and orders of analog PLLs have been analyzed and procedures for their design have been developed. Second-order analog PLLs have been analyzed by Hein and Scott [5] and Gardner [6]. Several other references [7]–[9] provide an analysis and design procedure for third-order charge-pump PLLs (CPPLLs). But there is only limited research

The authors are with the School of Electrical Engineering and Computer Science, Oregon State University, Corvallis, OR 97331 USA (e-mail: vova@eecs. oregonstate.edu).

Digital Object Identifier 10.1109/TCSII.2006.889443

Fvco PD LF VCO

Fig. 1. Analog PLL.

Fig. 2. All-digital PLL.

dedicated to the analysis of all-digital PLLs (ADPLLs). Phasedomain ADPLLs have been analyzed in [2] and [10]. In [11], the root locus technique has been applied to analyze the effect of the digital loop filter parameters on the bandwidth and stability of an ADPLL. However, none of these publications presents a procedure for designing an all-digital PLL given required bandwidth and phase margin specifications.

This brief is focused on a design approach for type-II secondorder all-digital PLLs and forms the basis for a systematic design procedure starting from the ADPLL specifications. In general, the proposed approach can be extended for the design of all-digital PLLs with different types and orders.

The brief is organized as follows. Section II gives an overview of typical all-digital PLLs. The discussion on the importance of the time-to-digital converter (TDC) resolution is given in Section III. In Section IV, a design flow for the ADPLL is described. A design example of a second-order all-digital PLL is presented in Section V. Finally, conclusions are provided in Section VI.

## II. OVERVIEW OF ALL-DIGITAL PLLS

A simplified block diagram of the all-digital PLL for a microprocessor or serial link application is shown in Fig. 2. It consists of a phase-to-digital converter (P2D), a digital loop filter (LF), a digitally controlled oscillator (DCO), and a feedback divider. The P2D senses the phase difference between the reference clock  $F_{\text{REF}}$  and the DCO divided clock  $F_{\text{CKV}}$  and converts it to a digital format. This information is filtered by the first-order digital LF and then is used to control the DCO. In the

Manuscript received August 8, 2006; revised October 19, 2006. This work was supported by the Semiconductor Research Corporation under Contract 2003-HJ-1076a and 2005-HJ-1326a. This paper was recommended by Associate Editor A. I. Karsilavan.

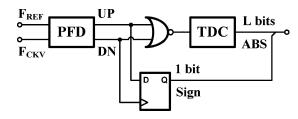

Fig. 3. Typical implementation of a P2D converter.

case of a ring-oscillator-based DCO, frequency tuning can be performed by digitally turning on and off bias current sources. When an *LC*-based DCO is employed, frequency tuning is done by switching on and off the tank capacitors. The P2D can be implemented in many different ways. One way, shown in Fig. 3, features a conventional phase/frequency detector (PFD) followed by a time-to-digital converter. It is beneficial to use a PFD instead of just a phase detector in order to expand the frequency lock range. The PFD produces up (UP) and down (DN) pulses. They are overlapped by an OR gate to create a pulse, the width of which is proportional to the absolute value of the phase error. The width of this pulse is digitized by a TDC with a resolution  $\Delta_{\text{TDC}}$  and an *L*-bit output ABS is produced. The D-flip-flop samples the UP pulse on the rising edge of the DN pulse. In this manner, the sign of the phase/frequency error can be determined.

The ADPLL of Fig. 2 has a structure and operation very similar to a second-order CPPLL. The principal difference is that the phase error information is processed in different domains. In the all-digital PLL, the UP and DN pulses are overlapped, and the result is digitized and processed by a digital filter. For the CPPLL, a charge pump (CP) is used to generate a charge which is proportional to the time difference between the UP and DN pulses. The resulting charge is pumped into the analog filter, the output voltage of which controls the VCO. This similarity allows one to extend the design procedure for a second-order CPPLL to a second-order ADPLL.

#### **III. TDC RESOLUTION**

The operation of an ADPLL fully depends on the TDC resolution, since it defines the resolution of the phase detector. Assuming that the period of the reference signal  $T_{\text{REF}}$  remains unchanged over time, the time resolution of the TDC can be converted in to a phase resolution of the phase-to-digital converter as

$$\Delta \Phi_{\rm P2D} = \frac{2\pi \Delta_{\rm TDC}}{T_{\rm REF}}.$$

(1)

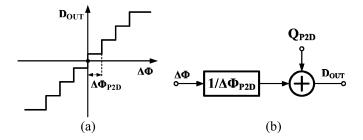

Fig. 4(a) shows a representative characteristic of the P2D, where the input phase difference is noted as  $\Delta\Phi$ . The relation between  $\Delta\Phi$  and the phase resolution of the P2D determines the applicability of a linear analysis for the ADPLL. If the input phase error  $\Delta\Phi$  is smaller than the resolution of the P2D converter, the behavior of the P2D is no different from a bang-bang phase detector. A linear analysis is not applicable in this case, and thus the bandwidth in a strict sense is not defined. The interested reader is referred to [12] for further discussion on this topic.

Fig. 4. (a) Transfer characteristic of P2D. (b) Linear model of P2D.

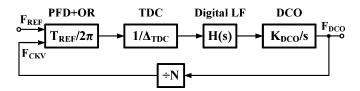

Fig. 5. s-domain approximation of the ADPLL.

On the other hand, if the input phase error  $\Delta \Phi$  is much larger than the resolution of the P2D converter, the input phase error is digitized in a linear manner. The P2D can be modeled as a gain of  $1/\Delta \Phi_{P2D}$  plus quantization noise as in Fig. 4(b). Having a linear phase detector allows us to use linear techniques for the analysis of ADPLLs. The noise contribution of a TDC is given in [13].

#### IV. DESIGN FLOW FOR AN ADPLL

It is beneficial to have a clear procedure for calculating the ADPLL parameters. Given a set of specifications, which usually include the phase margin (PM), the unity gain bandwidth  $(\omega_{\rm UGBW})$ , and the reference frequency  $(F_{\rm REF})$ , a designer should choose the loop filter parameters. This task can be accomplished by comparing *s*-domain models for digital and charge-pump PLLs. A conventional CPPLL has three poles and a zero. The third pole is introduced in order to attenuate the ripple which appears due to the nature of the CPPLL. In all-digital PLLs, this problem does not exist, and a second-order PLL is sufficient.

### A. s-domain Model for a Second-Order ADPLL

An *s*-domain approximation for the second-order ADPLL is shown in Fig. 5. The phase-frequency detector together with the OR gate converts the input phase error into an output pulse of width  $\Delta t$ . The transfer function of the PFD can be approximated as

$$PFD(s) = \frac{T_{REF}}{2\pi}.$$

(2)

The pulsewidth  $\Delta t$  is digitized by a time-to-digital converter with a resolution of  $\Delta_{TDC}$ . Usually, the resolution of the TDC is limited to one inverter delay and is considered to be fixed in our design approach. The transfer function of this operation can be approximated as

$$TDC(s) = \frac{1}{\Delta_{TDC}}.$$

(3)

Fig. 6. s-domain model for a second-order CPPLL.

Combining (2) and (3), the joint PFD and TDC transfer function (P2D) can be obtained as

$$P2D(s) = \frac{T_{\text{REF}}}{2\pi\Delta_{\text{TDC}}}.$$

(4)

The phase error in the digital domain is filtered by a firstorder digital loop filter and then fed to the DCO with a transfer function given by

$$DCO(s) = \frac{K_{DCO}}{s}.$$

(5)

When comparing this model to the s-domain model for a second-order CPPLL (Fig. 6), it can be seen that they are the same if

$$I_{\rm CP} = \frac{T_{\rm REF}}{\Delta_{\rm TDC}}$$

$$K_{\rm VCO} = K_{\rm DCO}$$

$$Z(s) = H(s).$$

(6)

Thus, in order to design an ADPLL given a set of specifications, first a CPPLL can be designed. Then, the specific parameters of the ADPLL can be calculated based on the relationships given in (6).

#### B. Design of a Second-Order CPPLL

Let us consider  $I_{\rm CP}$  and  $K_{\rm VCO}$  as predetermined constants. For the ADPLL,  $I_{\rm CP}$  is equivalent to the ratio of a reference clock period  $T_{\rm REF}$  to the resolution of the TDC ( $\Delta_{\rm TDC}$ ), and  $K_{\rm VCO}$  is equivalent to  $K_{\rm DCO}$ . A loop filter for the second-order CPPLL consists of a capacitor and a resistor connected in series. The capacitor value C and the resistor value R are the only unknowns.

The open loop gain of the CPPLL in Fig. 6 is given by

$$LG(s) = \frac{I_{CP}}{2\pi} \frac{K_{VCO}}{s} \frac{1}{N} \frac{s + \omega_z}{s} R$$

(7)

where  $\omega_z$  is the zero frequency

$$\omega_z = \frac{1}{RC}.$$

(8)

The phase margin for this system is given by

$$PM = \arctan\left(\frac{\omega_{\text{UGBW}}}{\omega_z}\right). \tag{9}$$

From (9), the required zero frequency  $\omega_z$  can be found as

$$\omega_z = \frac{\omega_{\rm UGBW}}{\tan(\rm PM)}.$$

(10)

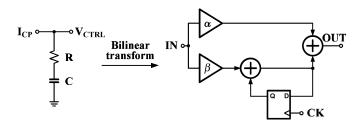

Fig. 7. Transform from an analog to a digital loop filter.

Based on  $|LG(j\omega_{UGBW})| = 1$ , the resistance value R can be found in a unique way as

$$R = \frac{2\pi N}{I_{\rm CP} K_{\rm VCO}} \frac{\omega_z^2}{\sqrt{\omega_z^2 + \omega_{\rm UGBW}^2}}.$$

(11)

Then, from (8) and (10), the capacitance value C is found to be

$$C = \frac{\tan(\text{PM})}{R\omega_{\text{UGBW}}}.$$

(12)

#### C. Calculation of the Digital Loop Filter Coefficients

A digital equivalent of an analog loop filter consists of a proportional path with a gain  $\alpha$  and an integral path with a gain  $\beta$ . The parameters of a digital loop filter  $\alpha$  and  $\beta$  can be obtained from the parameters of an analog loop filter R and C by using the bilinear transform (Fig. 7). The bilinear transform (13) is commonly used to design digital filters based on their analog prototypes [14]

$$s = \frac{2}{T_s} \frac{1 - z^{-1}}{1 + z^{-1}} \tag{13}$$

where  $T_s$  is the sampling time of a discrete-time system, which is the inverse of the reference frequency in our case.

Our goal is to preserve the frequency response and stability of the system; thus, the bilinear transform is an obvious choice. The only disadvantage of the bilinear transform is frequency warping. This affects the frequency response at frequencies close to the Nyquist rate. Since the bandwidth of the PLL is at least ten times smaller than the update rate, frequency warping will have a negligible effect.

The z-domain transfer function of the digital loop filter is given by

$$H(z) = \alpha + \beta \frac{1}{1 - z^{-1}} = \frac{(\alpha + \beta) - \alpha z^{-1}}{1 - z^{-1}}$$

(14)

where  $\alpha$  represents the proportional part and  $\beta$  represents the integral part of the loop filter gain.

The *s*-domain transfer function of the analog loop filter, given by (15), can be converted to the *z*-domain via the bilinear transform as follows:

$$Z(s) = \frac{V(s)}{I(s)} = R + \frac{1}{sC}$$

(15)

$$Z(s) \stackrel{s \to z}{=} \frac{\left(\frac{T_s}{2C} + R\right) + z^{-1}\left(\frac{T_s}{2C} - R\right)}{1 - z^{-1}}.$$

(16)

Comparing (14) and (16),  $\alpha$  and  $\beta$  can be found as

$$\alpha = R - \frac{T_s}{2C}$$

$$\beta = \frac{T_s}{C}$$

(17)

where  $\alpha$  and  $\beta$  are the only unknown parameters that need to be determined for the ADPLL design at this stage.

#### D. Relationship Between $\alpha$ and $\beta$

As a consequence of the analysis presented above, a simple relationship between the proportional gain  $\alpha$  and the integral gain  $\beta$  can be established. From (17), the ratio of  $\alpha$  to  $\beta$  is found to be

$$\frac{\alpha}{\beta} = \frac{RC}{T_s} - \frac{1}{2}.$$

(18)

Then, R and C from (11) and (12), respectively, are substituted into (18) to yield

$$\frac{\alpha}{\beta} = \frac{1}{T_s} \frac{\tan(\text{PM})}{\omega_{\text{UGBW}}} - \frac{1}{2}.$$

(19)

Given that  $T_s = 1/F_{\text{REF}}$  and  $\omega_{\text{UGBW}} = 2\pi F_{\text{UGBW}}$ , (19) can be expressed as

$$\frac{\alpha}{\beta} = \frac{F_{\text{REF}}}{F_{\text{UGBW}}} \frac{\tan(PM)}{2\pi} - \frac{1}{2}.$$

(20)

It can be seen from (20) that, for the given ADPLL reference frequency  $F_{\rm REF}$  and the unity gain bandwidth  $F_{\rm UGBW}$ , the  $\alpha$ -to- $\beta$  ratio defines the phase margin and thus the stability of a system.

#### V. DESIGN EXAMPLE

To validate the proposed approach, an all-digital PLL with the following specifications has been designed:

- phase margin  $PM = 45^{\circ}$ ;

- unity gain bandwidth  $F_{\text{UGBW}} = 1 \text{ MHz};$

- reference frequency  $F_{\text{REF}} = 80 \text{ MHz}$ ;

- feedback divider N = 16;

- DCO gain  $K_{\rm DCO} = 1$  MHz/LSB; ٠

- TDC resolution  $\Delta_{\text{TDC}} = 20$  ps.

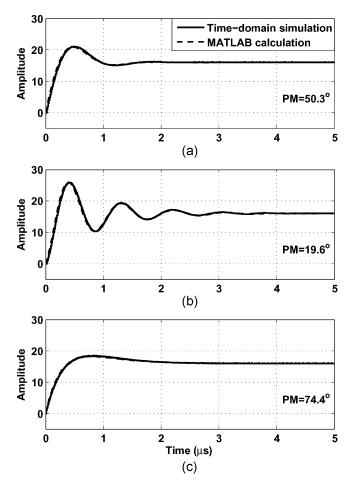

The phase margin has been intentionally chosen to be  $45^{\circ}$  in order to have ringing in the PLL's step response. This allows for better visual comparison of the step responses obtained by different methods. If a conventional inverter chain-based TDC is used, fine resolution ( $\Delta_{TDC} = 20 \text{ ps}$ ) is possible only in a deep-submicrometer CMOS process. There are other types of TDC as in [15] and [16] which can overcome this limitation.

The calculation starts with (10) from which, using the specifications for the unity gain bandwidth and phase margin, the required zero frequency is found to be  $\omega_z = 6.28 \cdot 10^6$  rad/s. Given the DCO gain  $K_{\text{DCO}}$ , the resolution of the TDC,  $\Delta_{\text{TDC}}$ , and the period of the reference clock  $T_s = 1/F_{\text{REF}}$ ,  $I_{\text{CP}}$  and  $K_{\rm VCO}$  are determined from (6). Based on that, the equivalent resistance  $R = 1.14 \cdot 10^{-1} \Omega$  is calculated from the (11). Then, the equivalent capacitance  $C = 1.4 \cdot 10^{-6}$  F is determined using (12). Finally, the digital loop filter parameters  $\alpha$  and  $\beta$  have been determined from (17). For easy hardware implementation, the

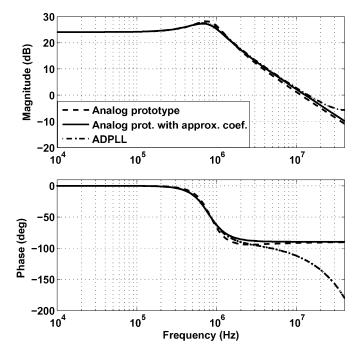

Fig. 8. Magnitude and phase responses of the ADPLL.

coefficients of the digital loop filter have to be approximated as power of two values:

- $\alpha = 1.09 \cdot 10^{-1} \cong 2^{-3};$   $\beta = 8.93 \cdot 10^{-3} \cong 2^{-7}.$

The above approximation affects the effective loop bandwidth and phase margin of the designed ADPLL. For the designed ADPLL, the effective phase margin is  $PM = 50.3^{\circ}$ and the effective unity gain bandwidth is UGBW = 1.01 MHz.

The magnitude and phase responses of the analog prototype, the analog prototype with coefficients approximated for the digital implementation, and the resulting ADPLL have been calculated and are shown in Fig. 8.

In Fig. 8, peaking of the magnitude responses is due to the low phase margin. An s-domain prototype inaccurately models an ADPLL at frequencies close to the Nyquist rate; thus, there are differences between the frequency responses at higher frequencies. Since the unity gain bandwidth of the ADPLL is a factor of 80 smaller than its reference frequency, the phase and frequency responses of the analog prototype and the ADPLL transfer functions are in good agreement in the band of interest.

The step response has been used to validate the design. Fig. 9(a) shows two step responses obtained in different ways. The dashed line represents the step response calculated in MATLAB from the s-domain transfer function using the "step" function. The solid line shows the step response obtained by a time-domain simulation of the designed all-digital PLL in Simulink. It can be seen that the plots are in good agreement. This demonstrates that the designed ADPLL behaves similar to the initial s-domain prototype. The results from the time-domain simulation of the CPPLL are not shown in this figure because of ripples. However, the filtered step response matches the s-domain calculations.

Two additional all-digital PLLs for a target UGBW = 1 MHzand target phase margins of  $20^{\circ}$  and  $80^{\circ}$  have been designed.

Fig. 9. Step response for an all-digital PLL. (a)  $\rm PM=50.3^\circ.$  (b)  $\rm PM=19.6^\circ.$  (c)  $\rm PM=74.4^\circ.$

TABLE I SUMMARY OF ADPLL DESIGNS

| Target PM | α        | $\beta$  | $\frac{\alpha}{\beta}$ | PM             | UGBW, MHz |

|-----------|----------|----------|------------------------|----------------|-----------|

| 20°       | $2^{-4}$ | $2^{-6}$ | 4                      | 19.6°          | 1.16      |

| 45°       | $2^{-3}$ | $2^{-7}$ | 16                     | $50.3^{\circ}$ | 1.01      |

| 80°       | $2^{-3}$ | $2^{-9}$ | 64                     | 74.4°          | 0.81      |

Their step responses are shown in Fig. 9(b) and (c). Once again, it is seen that the *s*-domain prototype and the ADPLL behave similarly. Table I summarizes the loop filter parameters and the effective PM and UGBW for all three ADPLL designs.

# VI. CONCLUSION

In this brief, a simple and systematic procedure for the design of a second-order all-digital PLL has been presented. Closedform expressions have been derived for the digital loop filter parameters. Based on this analysis, an ADPLL can be easily designed from specifications. The procedure presented in this brief has been used for the design of a oversampled ( $F_{\text{REF}} \gg F_{\text{UGBW}}$ ) second-order all-digital PLL where the *s*-domain approximation has proven to be sufficiently accurate in the design of traditional/analog PLLs. A time-domain step response simulation is in good agreement with a calculation of the step response in MATLAB using the ADPLL transfer function.

#### REFERENCES

- R. B. Staszewski, D. Leipold, K. Muhammad, and P. T. Balsara, "Digitally controlled oscillator (DCO)-based architecture for RF frequency synthesis in a deep-submicrometer CMOS process," *IEEE Trans. Circuits Syst. II.*, vol. 50, no. 11, pp. 815–828, Nov. 2003.

- [2] R. B. Staszewski, J. L. Wallberg, S. Rezeq, C.-M. Hung, O. E. Eliezer, S. K. Vemulapalli, C. Fernando, K. Maggio, R. Staszewski, N. Barton, M.-C. Lee, P. Cruise, M. Entezari, K. Muhammad, and D. Leipold, "All-digital PLL and transmitter for mobile phones," *IEEE J. Solid-State Circuits*, vol. 40, no. 12, pp. 2469–2482, Dec. 2005.

- [3] J. Lin, B. Haroun, T. Foo, J.-S. Wang, B. Helmick, S. Randall, T. Mayhugh, C. Barr, and J. Kirkpatric, "A PVT tolerant 0.18 MHz to 600 MHz self-calibrated digital PLL in 90 nm CMOS process," in *Proc. IEEE Int. Solid-State Circuits Conf.*, San Francisco, CA, Feb. 2004, pp. 488–541.

- [4] N. D. Dalt, E. Thaller, P. Gregorius, and L. Gazsi, "A compact tripleband low-jitter digital *LC* PLL with programmable coil in 130-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 40, no. 7, pp. 1482–1490, Jul. 2005.

- [5] J. Hein and J. W. Scott, "z-domain model for discrete-time PLL's," *IEEE Trans. Circuits Syst.*, vol. 35, no. 11, pp. 1393–1400, Nov. 1988.

- [6] F. Gardner, "Charge-pump phase-lock loops," *IEEE Trans. Commun.*, vol. COM-28, no. 11, pp. 1849–1858, Nov. 1980.

- [7] I. I. Novof, J. Austin, R. Kelkar, D. Strayer, and S. Wyatt, "Fully integrated CMOS phase-locked loop with 15 to 240 MHz locking range and 50 ps jitter," *IEEE J. Solid-State Circuits*, vol. 30, no. 11, pp. 1259–1266, Nov. 1995.

- [8] J. Maneatis, "Low-jitter process-independent DLL and PLL based on self-biased techniques," *IEEE J. Solid-State Circuits*, vol. 31, no. 11, pp. 1723–1732, Nov. 1996.

- [9] P. K. Hanumolu, M. Brownlee, K. Mayaram, and U. Moon, "Analysis of charge-pump phase-locked loops," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 51, no. 9, pp. 1665–1674, Sep. 2004.

- [10] R. B. Staszewski and P. T. Balsara, "Phase-domain all-digital phaselocked loop," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 52, no. 3, pp. 159–163, Mar. 2005.

- [11] A. M. Fahim, "A compact, low-power low-jitter digital PLL," in Proc. Eur. Solid-State Circuits Conf., 2003, pp. 101–104.

- [12] J. Lee, K. S. Kundert, and B. Razavi, "Analysis and modeling of bangbang clock and data recovery circuits," *IEEE J. Solid-State Circuits*, vol. 39, no. 9, pp. 1571–1580, Sep. 2004.

- [13] R. B. Staszewski, S. Vemulapalli, P. Vallur, J. Wallberg, and P. T. Balsara, "Time-to-digital converter for RF frequency synthesis in 90 nm CMOS," in *Proc. RFIC Symp.*, Jun. 2005, pp. 473–476.

- [14] S. K. Mitra, Digital Signal Processing: A Computer-Based Approach. New York: McGraw-Hill, 2001.

- [15] P. Dudek, S. Szczepanski, and J. Hatfield, "A high-resolution CMOS time-to-digital converter utilizing a Vernier delay line," *IEEE J. Solid-State Circuits*, vol. 35, no. 2, pp. 240–247, Feb. 2000.

- [16] V. Kratyuk, P. K. Hanumolu, K. Ok, K. Mayaram, and U. Moon, "A digital PLL with a stochastic time-to-digital converter," in *Proc. Symp. VLSI Circuits*, Jun. 2006, pp. 38–39.