## **Mealy Outputs**

Mealy state machines in VHDL look nearly the same as Moore machines. The difference is in how the output signal is created.

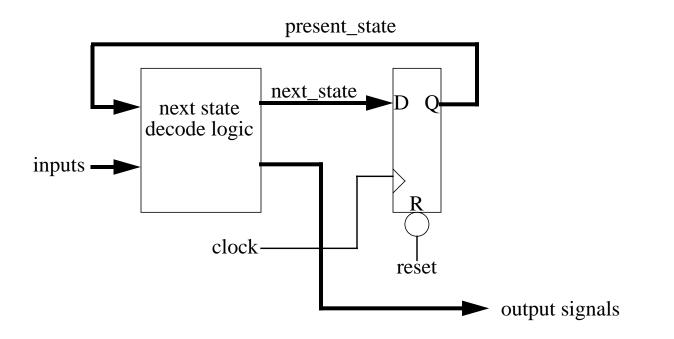

The general structure for a Mealy state machine. Here is the basic Mealy machine structure.

The Mealy state machine uses the next state decode logic to create the output signals. What makes an output a Mealy output is that it is a function of the input signals and the present state. A Mealy machine is really just a Moore machine with the outputs formed differently. As such, you may see a state machine with both Mealy and Moore outputs.

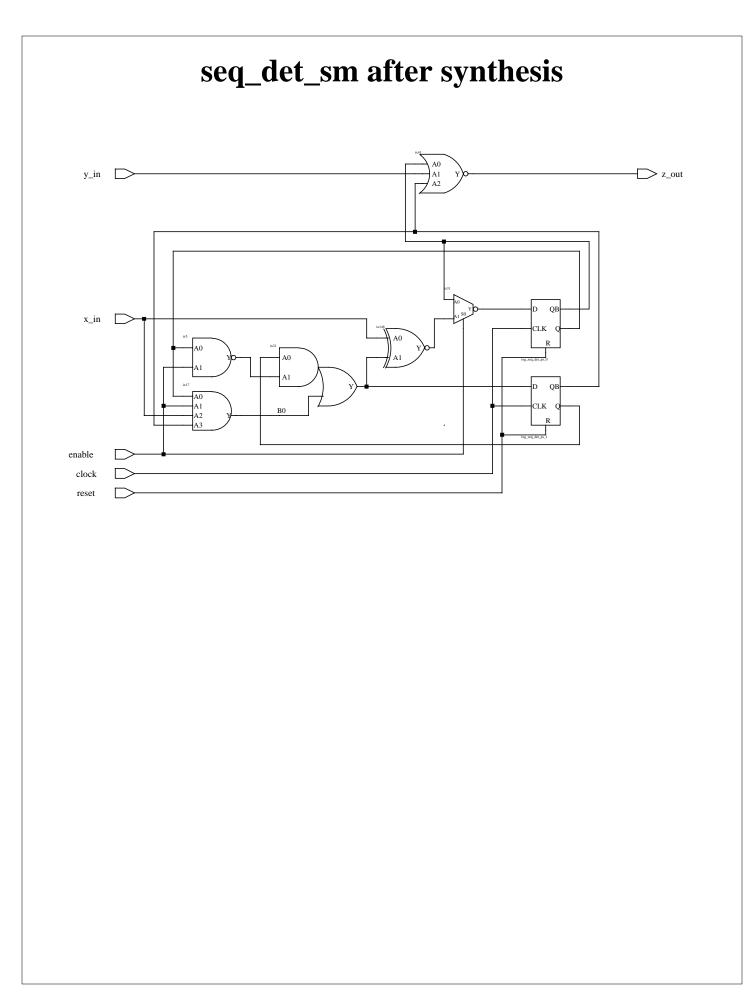

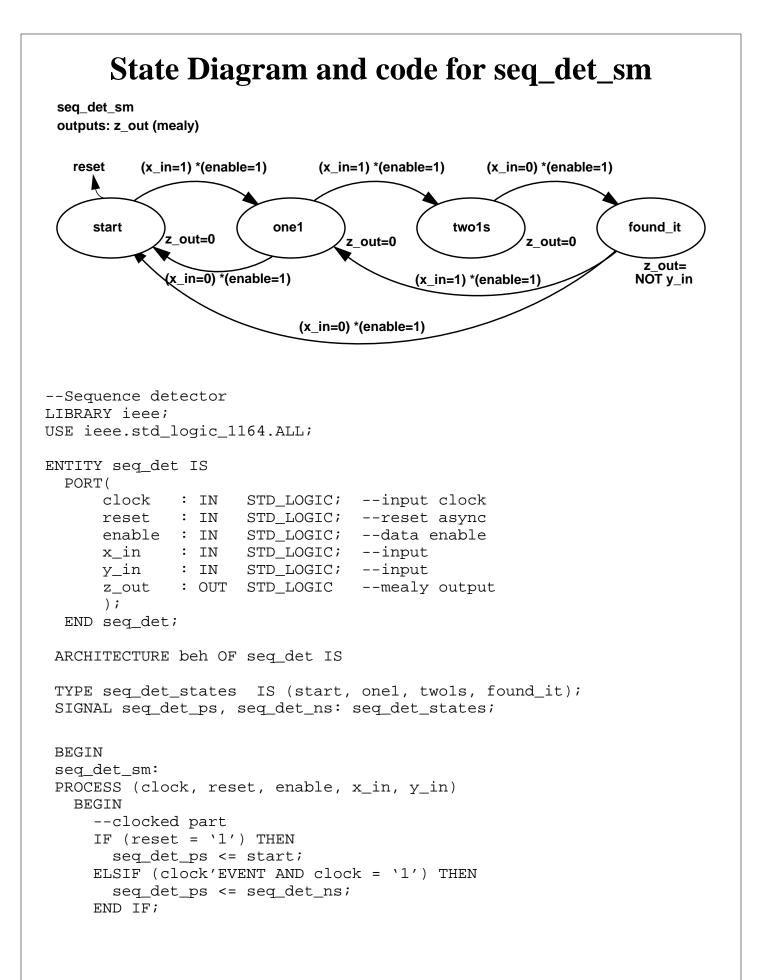

For an example, we will make the following state machine:

A sequence detector is to be built with inputs *clock*, *reset*, *enable*,  $x_in$ ,  $y_in$  and a single mealy output  $z_out$ . Once the machine is enabled, it searches for a sequence of "110" on the  $x_in$  input. When the "110" sequence is found, the value of  $z_out$  is equal to the complement of the  $y_in$  input.

Draw the state diagram and write the VHDL code for this state machine.

```

--combinatorial part

z_out <= `0'; --default value for mealy output</pre>

CASE seq_det_ps IS

WHEN start =>

IF ((x_in = '1') AND (enable = '1')) THEN

seq_det_ns <= one1;</pre>

ELSE

seq_det_ns <= start;</pre>

END IF;

WHEN onel =>

IF((x_in = '1') AND (enable = '1')) THEN

seq_det_ns <= two1s;</pre>

ELSIF((x_in = '0') AND (enable = '1')) THEN

seq_det_ns <= start;</pre>

ELSE

seq_det_ns <= one1;</pre>

END IF;

WHEN twols =>

IF((x_in = 0') AND (enable = 1')) THEN

seq_det_ns <= found_it;</pre>

ELSE

seq_det_ns <= two1s;</pre>

END IF;

WHEN found_it =>

z_out <= NOT y_in; -- mealy output</pre>

IF((x_in = '0') AND (enable = '1')) THEN

seq_det_ns <= start;</pre>

ELSIF((x_in = '1') AND (enable = '1')) THEN

seq det ns <= one1;</pre>

ELSE

seq_det_ns <= found_it;</pre>

END IF;

END CASE;

END PROCESS seq_det_sm;

END beh;

```