#### **Sample-and-Holds**

David Johns and Ken Martin University of Toronto (johns@eecg.toronto.edu) (martin@eecg.toronto.edu)

slide 1 of 18

© D.A. Johns, K. Martin, 1997

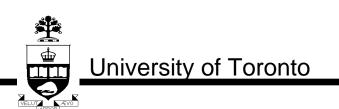

# Sample-and-Hold Circuits

- Also called "track-and-hold" circuits

- Often needed in A/D converters

- Conversion may required held signal

- Alsoreduces errors due to different delay times

#### **Errors in Sample-and-Holds**

- Sampling pedestal or Hold Step

- errors in going from track to hold

- should be signal independent for no distortion

- *Signal feedthrough* should be small during hold

- **Speed** due to bandwidth and slew-rate limitations

- *Droop rate* slow change during hold mode

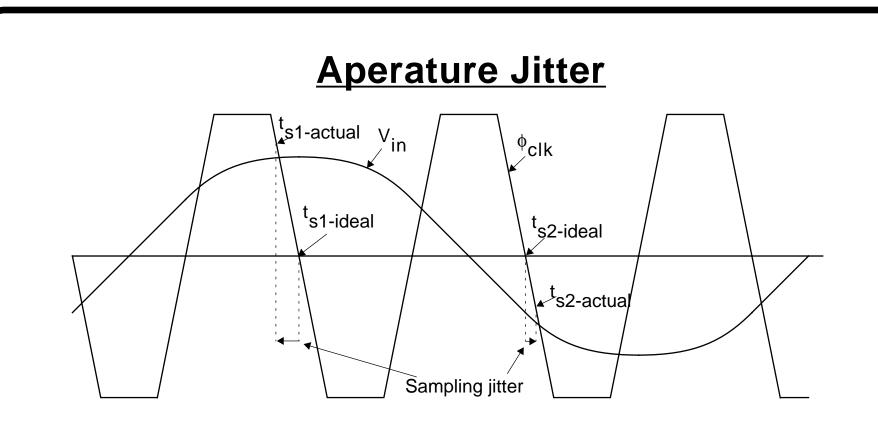

- Aperture (or sampling) jitter effective sampling time error in time; difficult in high-speed designs

University of Toronto

slide 2 of 18

- Basic circuit has some practical problems

Charge Injection

- Causes hold step

## **Aperature Jitter**

• Sampling time variation function of Vin

slide 3 of 18

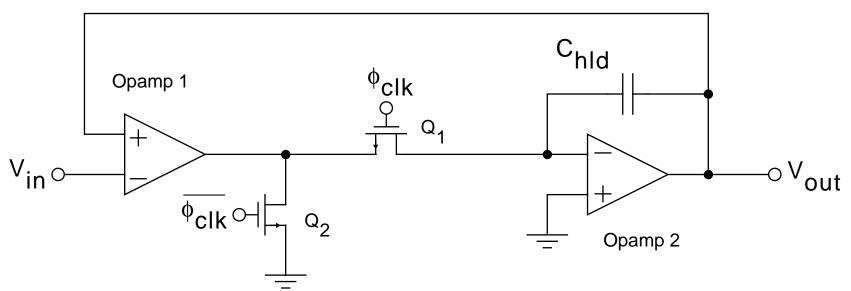

#### **Charge Injection**

- When φ<sub>clk</sub> goes low, channel charge on Q<sub>1</sub> causes V' to have negative step.

- If clock edge fast, 1/2 flows each way.

- Channel charge

$$\Delta Q_{C_{hld}} = \frac{Q_{\mathsf{CH}}}{2} = \frac{C_{ox}WLV_{eff-1}}{2} \tag{1}$$

$$V_{eff-1} = V_{GS1} - V_{tn} = V_{DD} - V_{tn} - V_{in}$$

(2)

resulting in

$$\Delta V' = \frac{\Delta Q_{C-hld}}{C_{hld}} = -\frac{C_{ox}WL(V_{DD} - V_{tn} - V_{in})}{2C_{hld}}$$

(3)

slide 4 of 18

© D.A. Johns, K. Martin, 1997

### **Charge Injection**

- $\Delta V'$  linearly related to  $V_{in}$  gain error

- $\Delta V'$  also linearly related to  $V_{tn}$ , which is nonlinearly related to  $V_{in}$  *distortion error*

- Often gain error can be tolerated but not distortion

• Also change due to the overlap capacitances

$$\Delta V' \cong -\frac{C_{ox}WL_{ov}(V_{DD} - V_{SS})}{C_{hld}}$$

(4)

• Causes dc offset effect

slide 5 of 18

- Q1 turns off when clock falls to within  $V_{tn}$  of  $V_{in}$

- True sampling time depends on value of  $V_{in}$  *distortion*

slide 6 of 18

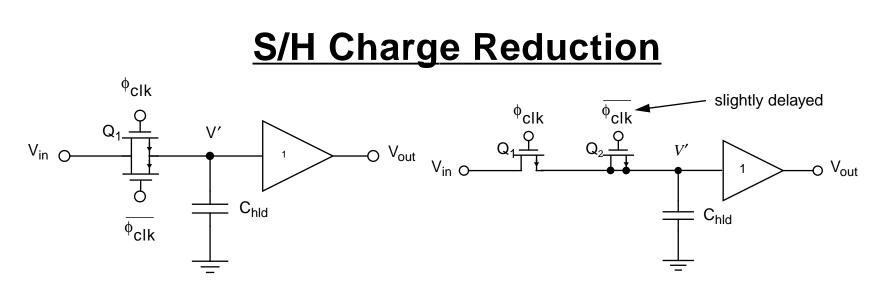

**CMOS transmission gate**

**Dummy switch**

- Transmission gate difficult to make p and n transistors match

- Dummy switch

- Q2 is 1/2 size of Q1 to match charge injection

- difficult to make clocks fast enough so exactly 1/2 charge is injected

- up to 5 times better than without dummy

slide 7 of 18

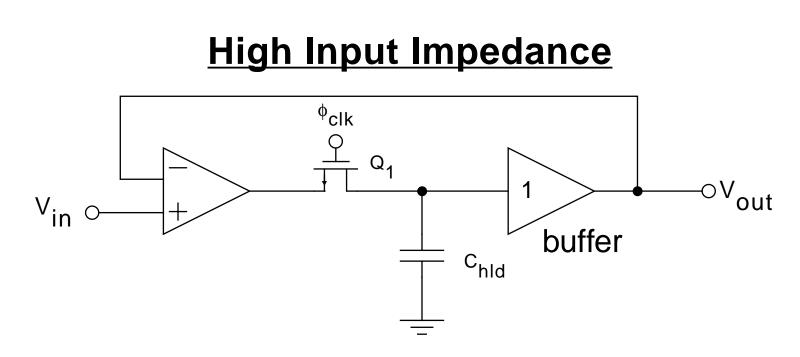

- dc offset of buffer divided by loop gain

Disadvantages

- Opamp output must have fast slew rate

- Samp time, charge inject input signal dependent

- Speed reduced due to overall feedback

slide 8 of 18

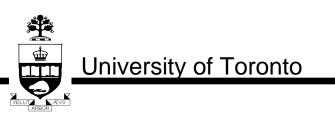

• Samp time, charge injection - input signal dependent

slide 9 of 18

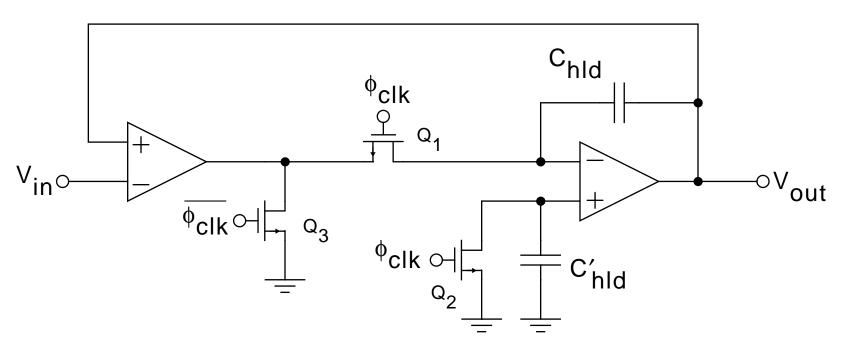

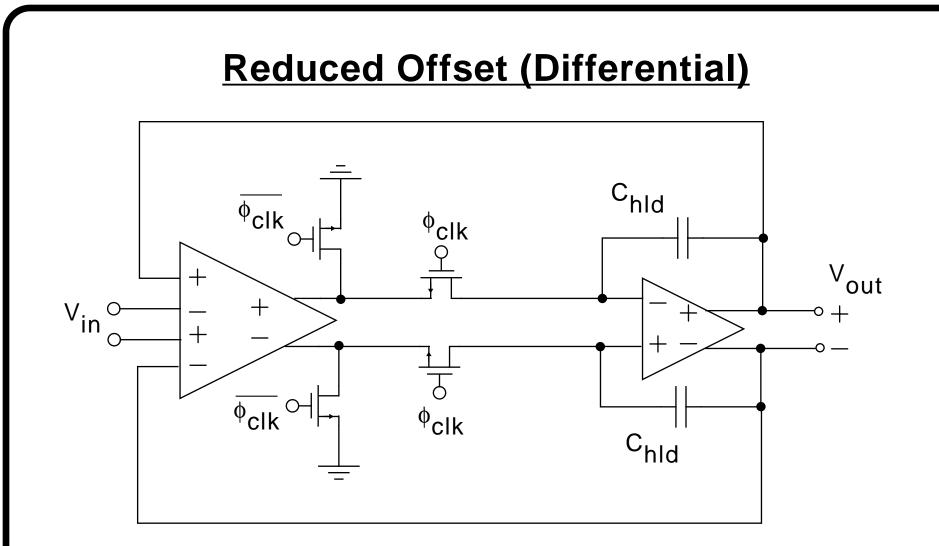

## Input Signal Independence

- Q1 always at virtual ground

- Samp time, charge injection NOT dependent

- Charge injection causes ONLY dc offset

- Q2 used to clamp opamp1 output near ground

- *Slower* due to two opamps in feedback

slide 10 of 18

### **Reduced Offset (Single Ended)**

- Charge injected by Q1 matched by Q2 into c'<sub>hld</sub>

- If fully differential design, matching occurs naturally leading to lower offset.

slide 11 of 18

• Gnd is common mode voltage

slide 12 of 18

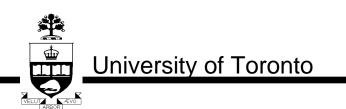

- Needs opamp capable of driving resistive loads

- Good high-speed BiCMOS configuration

- $\omega_{-3 \text{ dB}} = 1/(RC)$  when in track mode

- Might add a small input capacitor

University of Toronto

Ť

slide 13 of 18

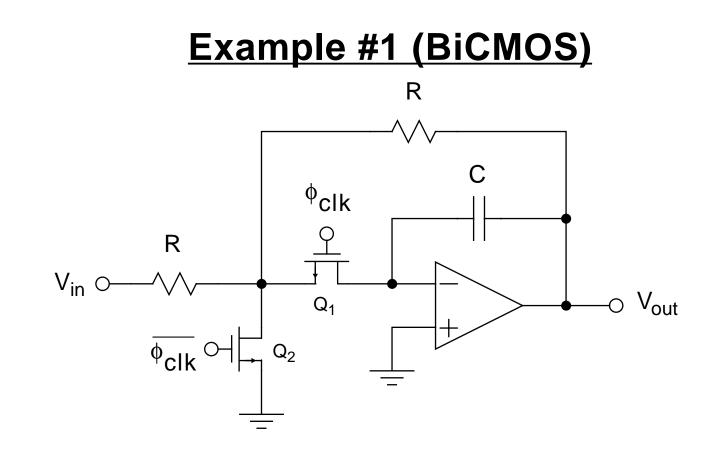

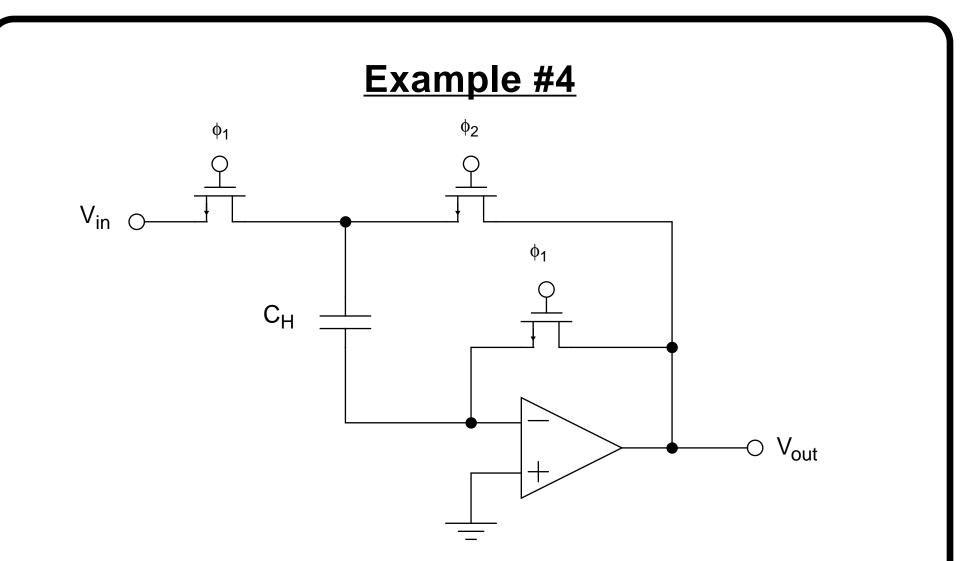

- Charge injection of transistors cancel

- Clock signals are signal dependent

- Good speed, moderate accuracy

University of Toronto

slide 14 of 18

- Hold capacitor is large Miller capacitor

- Can use smaller capacitors and switches good speed

- If Q2 turned off first, injection of Q1 small due to Miller effect

University of Toronto

Ť

slide 15 of 18

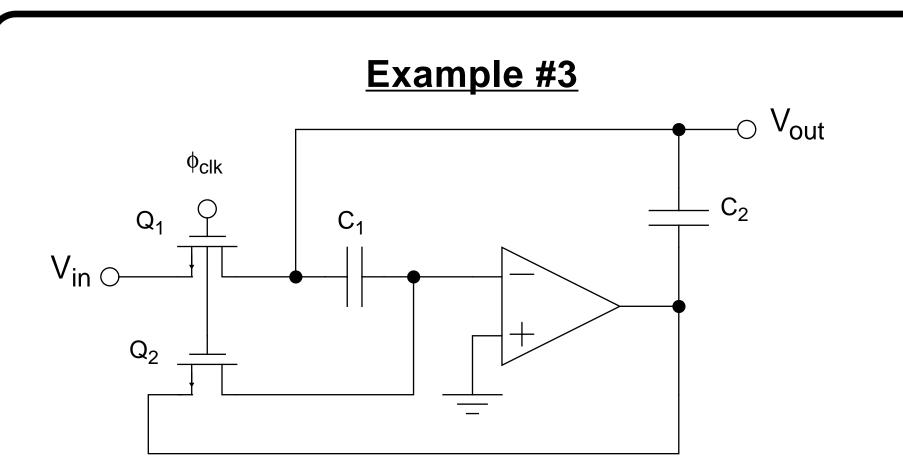

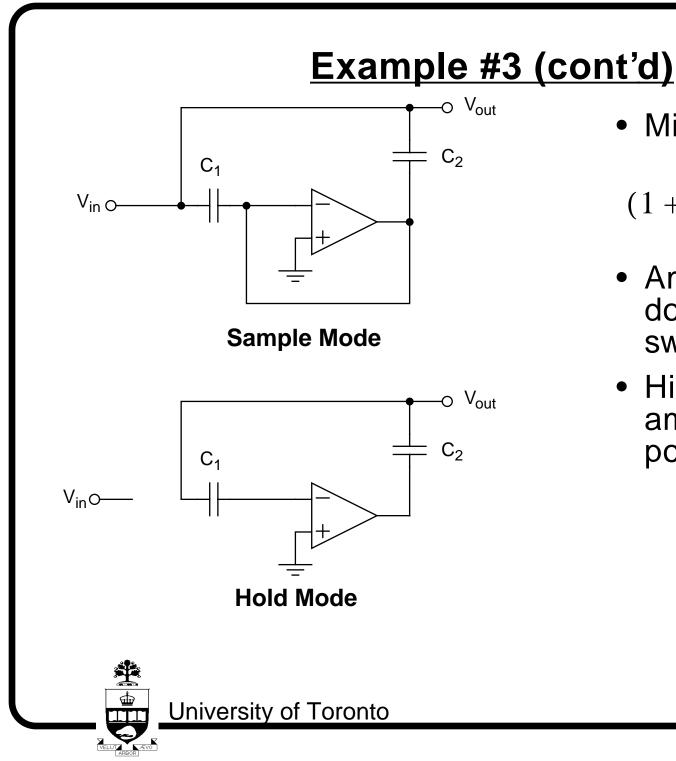

• Miller cap

$$(1+A)\left(\frac{C_1C_2}{C_1+C_2}\right)$$

- Amp output does not swing much

- Higher speed amplifier possible

slide 16 of 18

- Accurate since offset cancellation performed

- Slow since opamp swings from 0 to Vin every cycle

slide 17 of 18

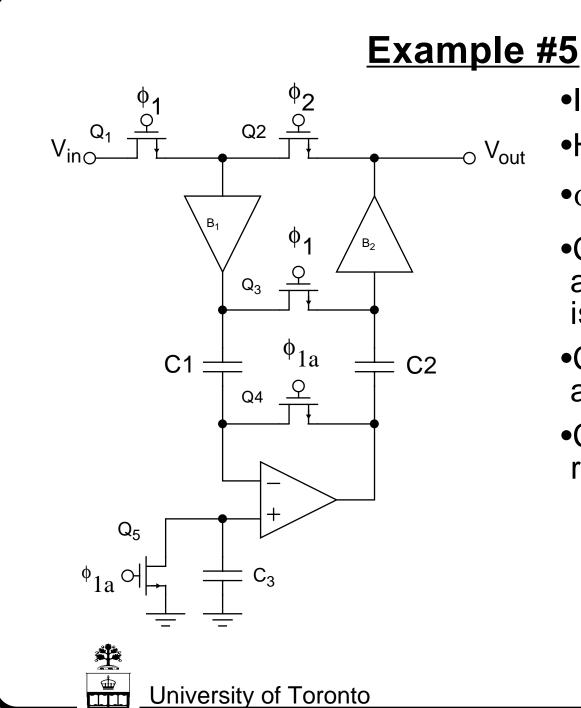

- Improved accuracy

- High input imped

- • $\phi_{1a}$  -> advanced

- •Charge inj of Q4 and Q5 cancel (and is signal indep)

- Charge inj of Q1 and Q2 - no effect

- Charge inj of Q3 reduced as before

slide 18 of 18