# A 0.951 ps<sub>rms</sub> Period Jitter, 3.2% Modulation Range, DSM-Free, Spread-Spectrum PLL

Hyuk Sun, Kazuki Sobue<sup>†</sup>, Koichi Hamashita<sup>†</sup>, Tejasvi Anand and Un-Ku Moon Electrical Engineering and Computer Science, Oregon State University, Corvallis, OR 97330, USA <sup>†</sup>Asahi Kasei Microdevices Corporation, Atsugi, Kanagawa 2430021, Japan

Abstract - This work presents a delta-sigma modulator free in-loop-bandwidth spread-spectrum clock generator. The proposed charge-based discrete-time loop filter with a digital-tocurrent converter enables wide range spread-spectrum frequency modulation with significantly relaxed PVT sensitivity. A correlated double sampling technique is leveraged to minimize 1/f noise in the proposed discrete-time loop filter. This work achieves 3.2% spread-spectrum modulation range and 26.51dB spectrum attenuation at 352MHz output frequency. A 142% change in  $K_{VCO}$  results in less than 298ppm modulation range error. Implemented in a 0.18 $\mu$ m CMOS, this work achieves 951fs<sub>rms</sub> period jitter while consuming 9.93mW with a 1.8V supply.

### Keywords - phase-locked loop, spread-spectrum clocking.

## I. INTRODUCTION

Spread-spectrum clock (SSC) generation is known to be a primary way to manage electromagnetic interference (EMI) issues in consumer products. One such system is a multifunctional print module, which requires an exceptionally demanding SSC specification such as more than 3% modulation range ( $\Delta f_{SSC\_range}$ ) with 10kHz modulation rate ( $f_{SSC\_rate}$ ) on multiple clock phases.

There are three popular ways to create a spread spectrum modulation: (1) out-of-loop-bandwidth direct SSC modulation, (2) in-loop-bandwidth SSC modulation, and (3) two-point SSC modulation. In the out-of-loop-bandwidth direct modulation technique, the SSC modulation signal directly modulates the control voltage of a voltage-controlled oscillator (VCO) [1]. Because this SSC modulation signal is injected above the loop bandwidth (BW), this scheme requires narrow loop BW, which results in prohibitively large loop filter and limited suppression of VCO noise. Another critical drawback of the direct modulation technique arises because the modulation range changes as the VCO gain ( $K_{VCO}$ ) varies due to PVT variations.

The in-loop-bandwidth SSC modulation technique employs either frequency domain SSC modulation with a delta-sigma modulator (DSM) [2] or phase domain SSC modulation with a time-to-digital converter (TDC) in all-digital PLLs [3]-[4]. In this technique, the SSC modulation rate is inside the PLL loop BW. The in-loop-bandwidth SSC technique can achieve robust SSC frequency modulation with respect to PVT variations. This is due to the fact that both the DSM based fractional frequency divider and the digitally controlled phase accumulation guarantees the desired frequency division ratio between the input reference frequency ( $f_{REF}$ ) and the output

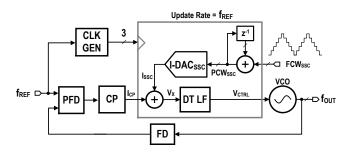

Fig. 1. Proposed spread-spectrum PLL block diagram.

frequency (f<sub>OUT</sub>). To achieve both faster SSC modulation rate and larger suppression of the VCO phase noise requires wide PLL loop BW. In case of the DSM based SSC modulators, wide loop BW results in an increase of the in-band shaped DSM noise and in-band spurious tones. In case of phase domain SSC modulation scheme in all-digital PLLs, wide loop BW increases quantization noise from the TDC and digitally controlled oscillator. One can avoid the problem by reducing the loop BW with a low noise LC VCO instead of a ring VCO. However, limited frequency tuning range, area overhead, and inability to create multiple output phases limit the use of the LC VCO for the desired application.

The two-point SSC modulation technique is a combination of both the out-of-loop-bandwidth and in-loop-bandwidth SSC modulation techniques [5]. Two-point SSC modulation technique breaks the trade-off between the PLL loop BW and the modulation rate. However, matching the SSC modulation gains for two different modulation injection points is not trivial, and the out-of-loop-bandwidth SSC modulation gain is still susceptible to the PVT variations of the K<sub>VCO</sub>.

In view of these limitations of the existing techniques, we present a 352MHz in-loop-bandwidth ring oscillator based SSC generator with a charge-based discrete-time loop filter. Without using a DSM or TDC, the proposed PLL achieves 3.2% in-loop-bandwidth SSC modulation, with significantly reduced PVT sensitivity. The proposed SSC scheme and the correlated double sampling scheme are discussed in Section-III. The measurements and conclusions are given in Section-III and -IV, respectively.

### II. PROPOSED SSC ARCHITECTURE

Fig.1 shows the block diagram of the proposed spreadspectrum PLL. This proposed architecture consists of phase frequency detector (PFD), charge pump (CP), discrete time

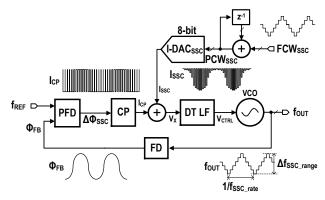

Fig. 2. Proposed in-loop-bandwidth SSC modulation technique.

loop filter (DT-LF), SSC return-to-zero (RZ) current digital-toanalog converter (I-DAC<sub>SSC</sub>), digital integrator, ring VCO, and frequency divider (FD). The CLK GEN block creates three clock phases for the DT-LF and I-DAC<sub>SSC</sub> at the rate of  $f_{REF}$ . The SSC frequency control word (FCW<sub>SSC</sub>) is a triangular spread-spectrum modulation signal, and this FCW<sub>SSC</sub> is digitally accumulated to convert to a phase domain modulation signal (PCW<sub>SSC</sub>). This accumulated PCW<sub>SSC</sub> drives the I-DAC<sub>SSC</sub>, which injects the phase domain spread-spectrum modulation signal inside the loop. The charge-based DT-LF combines both the I-DAC<sub>SSC</sub> modulation current (I<sub>SSC</sub>) and charge pump current (I<sub>CP</sub>), and updates V<sub>CTRL</sub>.

#### A. Proposed In-Loop-Bandwidth SSC Modulation

Fig. 2 shows the proposed in-loop-bandwidth SSC modulation technique. The SSC modulation of the output clock is achieved by providing a triangular ramp on the FCW<sub>SSC</sub>. The digitally accumulated PCW<sub>SSC</sub> is converted to the return-tozero I<sub>SSC</sub> in I-DAC<sub>SSC</sub>. The magnitude is proportional to PCW<sub>SSC</sub> and the width is fixed to 50% of the reference period  $(T_{REF})$ . Due to the SSC frequency modulation of the VCO, a SSC phase difference ( $\Delta \phi_{SSC}$ ), which is the difference between the divided VCO phase output ( $\phi_{FB}$ ) and the input reference frequency phase ( $\phi_{REF}$ ), is created. This SSC phase difference  $\Delta \phi_{\rm SSC}$  results in the pulse-width modulated I<sub>CP</sub> at the output of the charge pump. Since this SSC charge pump current I<sub>SSC</sub> cancels a part of the I-DAC<sub>SSC</sub> current  $I_{CP}$ , the residual current is integrated and converted to a charge signal on a sampling capacitor in the proposed DT LF. This sampled charge signal is filtered to generate a triangular SSC signal at V<sub>CTRL</sub>, which modulates the VCO output frequency.

The input-output relationship of FCW<sub>SSC</sub> and VCO output frequency at low frequencies can be approximated as:

$$\frac{f_{OUT}}{FCW_{SSC}} \cong \frac{I_{SSC-LSB}/2}{I_{CP}/M} \times f_{REF}$$

(1)

where  $I_{SSC-LSB}$  is the least-significant bit current in the I-DAC<sub>SSC</sub>, and M is the frequency division ratio in the frequency divider. Please note that (1) does not depend on either design parameters in the proposed DT LF or K<sub>VCO</sub>. This is because any perturbations on them due to PVT variations are attenuated by the PLL loop gain. This is the key advantage of the proposed technique over the out-of-loop-bandwidth direct SSC and two-point SSC modulations, where any change in the K<sub>VCO</sub>

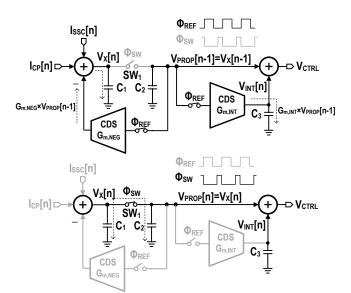

Fig. 3. The block and timing diagrams of the proposed charge-based DT LF.

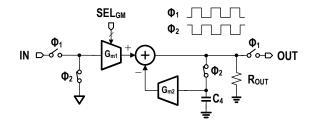

Fig. 4. The correlated double sampling scheme in the transconductors.

directly appears at the output. Therefore, the proposed technique achieves superior modulation in the presence of PVT variations without using either a DSM or TDC.

The maximum achievable frequency spread spectrum range is limited by the total accumulated  $\Delta \phi_{SSC}$  at the PFD input. For proper operation of this spread spectrum PLL, the  $\Delta \phi_{SSC}$  must not exceed the reference period  $T_{REF}$ . This is because the maximum range for effective phase cancellation from the charge pump and I-DAC<sub>SSC</sub> in the proposed DT LF is only  $\pm \pi$ . If the total accumulated  $\Delta \phi_{SSC}$  is greater than this limit, it could corrupt the next update sample in the proposed DT LF. Therefore, to achieve wider spread spectrum modulation range, one needs to use lower  $f_{REF}$ , indicating that  $f_{REF}$  is inversely proportional to the modulation range. Since the maximum loop BW is typically less than  $f_{REF}/10$  due to stability concern, lowering f<sub>REF</sub> reduces the maximum achievable loop BW and results in less suppression of the VCO phase noise. In this work, we demonstrate this trade-off by changing  $f_{REF}$  and measure the corresponding spread-spectrum modulation range.

In the proposed architecture, the loop filter input is the sum of  $I_{SSC}$  and  $I_{CP}$ . The  $I_{SSC}$  is a return-to-zero current pulse, whereas the  $I_{CP}$  is a pulse-width modulated current pulse. Filtering these two different types of current signals with a conventional passive loop filter creates unacceptable spurs at the output, which destroys the shape of the spread spectrum. Therefore, we propose a charge-based DT LF.

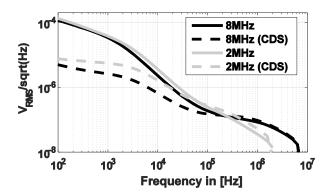

Fig. 5. The proposed DT LF sampled noise at  $V_{CTRL}$  for  $f_{REF}=2MHz$  and 8MHz, when the CDS is enabled and disabled.

Fig. 6. Die microphotograph.

## B. Proposed Charge-Based Discrete-Time Loop-Filter

Fig. 3 shows the block and timing diagrams of the proposed DT LF. It consists of two transconductors ( $G_{m,NEG}$  and  $G_{m,INT}$ ), three capacitors ( $C_1$ ,  $C_2$ , and  $C_3$ ), and three switches (SW<sub>1</sub>,  $SW_2$  and  $SW_3$ ). The negative feedback  $G_{m,NEG}$  is added to synthesize a stabilizing zero in the loop. This negative feedback loop also reduces the swing on the node  $V_{X}$ , improving the linearity of the charge pump and I-DAC<sub>SSC</sub>. In addition, the G<sub>m INT</sub> integral path makes the proposed PLL a Type-II PLL. The proposed DT LF operates in two phases:  $\phi_{\text{REF}}$  and  $\phi_{\text{SW}}$ . During  $\phi_{\text{REF}}$ , the currents from I<sub>SSC</sub>[n], I<sub>CP</sub>[n], and the negative feedback current  $(G_{m NEG} \times V_{PROP}[n-1])$  are accumulated on the capacitor  $C_1$ . At the same time, the SW<sub>3</sub> is closed and the current from  $G_{m INT}$  ( $G_{m INT} \times V_{PROP}[n-1]$ ) is integrated on the capacitor C<sub>3</sub>. During  $\phi_{SW}$ , the voltage V<sub>X</sub>[n] on capacitor  $C_1$  is transferred to  $C_2$  ( $C_1 \approx 10C_2$ ). This switched mode operation of the proposed DT LF helps to isolate the node V<sub>CTRL</sub> from the large transients, which appear at node V<sub>X</sub> during  $\phi_{\text{RFF}}$ . Therefore, with the help of linear charge domain signal filtering, the proposed DT LF achieves in-loopbandwidth phase domain SSC modulation without a DSM.

## C. Correlated Double Sampling (CDS) Transconductor

The use of active elements in the proposed DT LF results in undesirable offset and 1/f noise. Therefore, the correlated double sampling scheme in [6] is implemented in  $G_{m,NEG}$  and  $G_{m,INT}$  blocks, as shown in Fig. 4. The CDS transconductor consists of the main and auxiliary transconductor  $G_{m1}$  and  $G_{m2}$

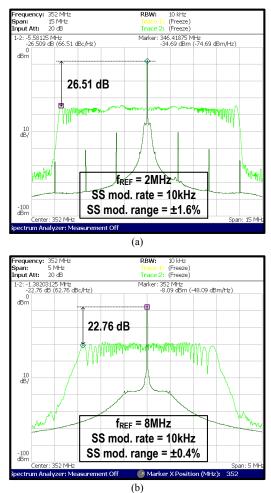

Fig. 7. Output spectrum when the SSC is enabled and disabled for: (a)  $f_{\rm REF}{=}2MHz,$  (b)  $f_{\rm REF}{=}8MHz.$

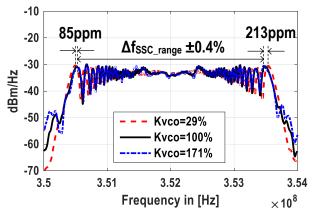

Fig. 8. Measured SSC output spectra for various K<sub>VCO</sub> values in f<sub>REF</sub>=8MHz.

with a sampling capacitor C<sub>4</sub>. First, the auxiliary  $G_{m2}$  forms a negative feedback to sample the offset and 1/f noise during  $\phi_2$ . Then the auxiliary  $G_{m2}$  loop compensates the sampled offset and 1/f noise during  $\phi_1$ . Fig. 5 shows the simulated sampled noise at node  $V_{CTRL}$  for two different reference frequencies ( $f_{REF}=2MHz$  and 8MHz). When the CDS scheme is enabled, a significant reduction of 1/f noise is observed for both references.

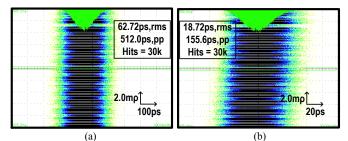

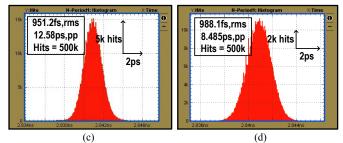

Fig. 9. Absolute jitter measurements for: (a)  $f_{REF}=2MHz$ , (b)  $f_{REF}=8MHz$ .

Fig. 10. Period jitter measurements for: (a)  $f_{REF}=2MHz$ , (b)  $f_{REF}=8MHz$ .

|                             | This work         |       | [2]             | [4]              | [3]              |

|-----------------------------|-------------------|-------|-----------------|------------------|------------------|

| Architecture                | Integer-N         |       | FractN          | AD-PLL           | AD-PLL           |

| Technology                  | 180nm             |       | 150nm           | 65nm             | 22nm             |

| f <sub>OUT</sub> [GHz]      | 0.352             |       | 1.5             | 0.375~3.0        | 0.6~3.6          |

| f <sub>ref</sub> [MHz]      | 2                 | 8     | 20~40           | 25               | 25~200           |

| SSC<br>Scheme               | In-LBW<br>(DT LF) |       | In-LBW<br>(DSM) | In-LBW           | In-LBW           |

| f <sub>SSC_rate</sub> [kHz] | ≥ 10              |       | ≥ 31.3          | $\geq$ 33        | $\geq 25$        |

| $\Delta f_{SSC\_range}$ [%] | 3.2               | 0.8   | 0.5             | 0.5              | 2                |

| EMI Atten<br>[dB]           | 26.5              | 22.76 | 20.3            | NA               | < 20             |

| Jitter type                 | Period            |       | 250 cycle       | Period           | N-cycle          |

| rms jitter<br>[ps,rms]      | 0.951             | 0.988 | 8.1             | 8.16             | 10.0             |

| P-P Jitter<br>[ps,pp]       | 12.6              | 8.49  | NA              | 75               | NA               |

| Supply [V]                  | 1.8               |       | 1.5             | 1.1              | 1.0              |

| Power [mW]                  | 9.93              |       | 54              | 2.92<br>(375MHz) | 18.4<br>(3.6GHz) |

| Area [mm <sup>2</sup> ]     | 3.01              |       | 0.42            | 0.38             | 0.29             |

| TARIFI | Summary | and cor | nnaricon | with | state-of-the-art |  |

|--------|---------|---------|----------|------|------------------|--|

## III. MEASUREMENT RESULTS

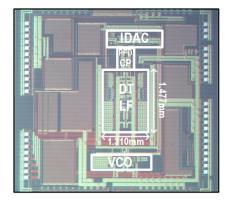

The proposed in-LBW SSC PLL was fabricated in a 0.18 $\mu$ m CMOS. The die micrograph is shown in Fig. 6. The proposed PLL consumes 9.93mW total power, while operating from a 1.8V supply. The proposed DT LF dissipates approximately 10% of the total power, and the power penalty due to the I-DAC<sub>SSC</sub> is less than 5% of the total power.

Fig. 7 shows the measured output spectra for both unmodulated and modulated modes. The SSC attenuation of 26.51dB ( $f_{REF}=2MHz$ ) and 22.76dB ( $f_{REF}=8MHz$ ) is achieved. When  $f_{REF}$  is increased from 2MHz to 8MHz, the maximum

$\Delta f_{SSC range}$  is reduced from ±1.6% to ±0.4%, and this reduction demonstrates the trade-off between  $T_{REF}$  and  $\Delta f_{SSC range}$ . To demonstrate PVT insensitive operation, measured SSC outputs are plotted in Fig. 8 for various  $K_{VCO}$  values. In  $f_{REF}$ =8MHz with the desired ±4000ppm modulation range, a 142% change (from 13.4 to 90.7MHz/volt in 53MHz/volt nominal K<sub>VCO</sub>) in  $K_{VCO}$  results in less than 298ppm change in  $\Delta f_{SSC range}$ . Measured absolute and period jitters for  $f_{REF}=2MHz$  and 8MHzare shown in Fig. 9 and Fig. 10, respectively. For f<sub>REF</sub>=8MHz, the absolute and period jitters are  $18.7 p s_{rms}$  and  $988 f s_{rms},$ respectively. For  $f_{REF}=2MHz$ , the absolute and period jitters are 62.7ps<sub>rms</sub> and 951fs<sub>rms</sub>, respectively. Finally, Table 1 summarizes the results and compares them with the state-ofthe-art PLLs which employ a ring VCO. Thanks to the proposed DT LF, operating at an order of magnitude lower f<sub>REF</sub>, the proposed PLL achieves an order of magnitude lower period jitter performance, without increasing the power consumption. This work achieves a 3.2%  $\Delta f_{SSC range}$  with 26.5dB attenuation using the 8-bit I-DAC<sub>SSC</sub>, whereas the work in [3] requires a 24-bit FCW<sub>SSC</sub> to deliver a 2%  $\Delta f_{SSC}$  range with less than 20dB attenuation.

## IV. CONCLUSIONS

This work proposes a DSM-free in-loop-bandwidth SSC modulation scheme. The proposed in-LBW scheme can maximize the LBW to increase the phase noise suppression of a ring VCO. The I-DAC<sub>SSC</sub> with the proposed charge-based DT LF establishes the wide spread-spectrum frequency modulation, and this work obtains significantly relaxed PVT sensitivity for the SSC modulation. Finally, the 1/f noise and offset of the proposed DT LF is cancelled using the CDS scheme. This work achieves a 3.2%  $\Delta f_{SSC_range}$  and 26.5dB spread-spectrum attenuation with sub-ps<sub>rms</sub> period jitter, while consuming 9.93mW with a 1.8V supply. The measured SSC range error is 298ppm with 142% K<sub>VCO</sub> variation.

#### REFERENCES

- H.S. Li, Y.C. Cheng, and D. Puar, "Dual-loop spread-spectrum clock generator," *ISSCC Dig. Tech. Papers*, pp. 184-185, 1999.

- [2] M. Kokubo, T. Kawamoto, T. Oshima, T. Noto, M. Suzuki, S. Suzuki, T. Hayasaka, T. Takahashi, and J. Kasai, "Spread-spectrum clock generator for serial ATA using fractional PLL controlled by ΔΣ modulator with level shifter," *ISSCC Dig. Tech. Papers*, pp. 160-161, 2005.

- [3] Y.W. Li, C. Ornelas, H.S. Kim, H. Lakdawala, A. Ravi, and K. Soumyanath, "A reconfigurable distributed all-digital clock generator core with SSC and skew correction in 22nm high-k tri-gate LP CMOS," *ISSCC Dig. Tech. Papers*, pp. 70-71, 2012.

- [4] W. Grollitsch, R. Nonis, N. Da Dalt, "A 1.4ps<sub>rms</sub>-Period-Jitter TDC-less fractional-N digital PLL with digitally controlled ring oscillator in 65nm CMOS," *ISSCC Dig. Tech. Papers*, pp. 478-479, 2010.

- [5] T.-H. Tsai, M.-H. Yuan, C.-H. Chang, C.-C. Liao, C.-C. Li, and R. B. Staszewski, "A 1.22ps integrated-jitter 0.25-tp-4GHz fractional-N ADPLL in 16nm FinFET CMOS," *ISSCC Dig. Tech. Papers*, pp. 260-261, 2015.

- [6] C. C. Enz and G. G. Temes, 'Circuit techniques for reducing the effects of op-amp imperfections: autozeroing, correlated double sampling, and chopper stabilization,' *Proc. IEEE*, vol. 84, no. 9, pp. 1584-1614, Nov. 1999.