# 18. RTC – Real-Time Counter

### 18.1 Features

- 16-bit resolution

- Selectable clock source

- 32.768kHz external crystal

- External clock

- 32.768kHz internal oscillator

- 32kHz internal ULP oscillator

- Programmable 10-bit clock prescaling

- One compare register

- One period register

- Clear counter on period overflow

- Optional interrupt/event on overflow and compare match

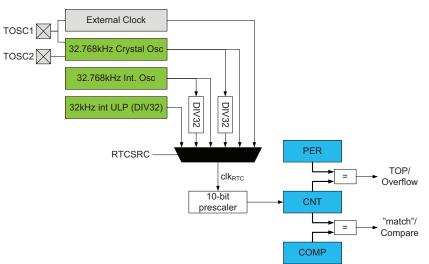

## 18.2 Overview

The 16-bit real-time counter (RTC) is a counter that typically runs continuously, including in low-power sleep modes, to keep track of time. It can wake up the device from sleep modes and/or interrupt the device at regular intervals.

The reference clock is typically the 1.024kHz output from a high-accuracy crystal of 32.768kHz, and this is the configuration most optimized for low power consumption. The faster 32.768kHz output can be selected if the RTC needs a resolution higher than 1ms. The RTC can also be clocked from an external clock signal, the 32.768kHz internal oscillator or the 32kHz internal ULP oscillator.

The RTC includes a 10-bit programmable prescaler that can scale down the reference clock before it reaches the counter. A wide range of resolutions and time-out periods can be configured. With a 32.768kHz clock source, the maximum resolution is 30.5µs, and time-out periods can range up to 2000 seconds. With a resolution of 1s, the maximum time-out period is more than18 hours (65536 seconds). The RTC can give a compare interrupt and/or event when the counter equals the compare register value, and an overflow interrupt and/or event when it equals the period register value.

#### Figure 18-1. Real-time counter overview.

# **Atmel**

#### 18.2.1 Clock Domains

The RTC is asynchronous, operating from a different clock source independently of the main system clock and its derivative clocks, such as the peripheral clock. For control and count register updates, it will take a number of RTC clock and/or peripheral clock cycles before an updated register value is available in a register or until a configuration change has effect on the RTC. This synchronization time is described for each register. Refer to "RTCCTRL – RTC Control register" on page 92 for selecting the asynchronous clock source for the RTC.

#### 18.2.2 Interrupts and Events

The RTC can generate both interrupts and events. The RTC will give a compare interrupt and/or event at the first count after the counter value equals the Compare register value. The RTC will give an overflow interrupt request and/or event at the first count after the counter value equals the Period register value. The overflow will also reset the counter value to zero.

Due to the asynchronous clock domain, events will be generated only for every third overflow or compare match if the period register is zero. If the period register is one, events will be generated only for every second overflow or compare match. When the period register is equal to or above two, events will trigger at every overflow or compare match, just as the interrupt request.

## 18.3 Register Descriptions

#### 18.3.1 CTRL – Control register

| Bit           | 7 | 6 | 5 | 4 | 3 | 2   | 1           | 0   |

|---------------|---|---|---|---|---|-----|-------------|-----|

| +0x00         | - | - | - | - | - | Р   | RESCALER[2: | 0]  |

| Read/Write    | R | R | R | R | R | R/W | R/W         | R/W |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0   | 0           | 0   |

#### Bit 7:3 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always write these bits to zero when this register is written.

#### Bit 2:0 – PRESCALER[2:0]: Clock Prescaling factor

These bits define the prescaling factor for the RTC clock according to Table 18-1 on page 214.

#### Table 18-1. Real-time counter clock prescaling factor.

| PRESCALER[2:0] | Group configuration | RTC clock prescaling          |

|----------------|---------------------|-------------------------------|

| 000            | OFF                 | No clock source, RTC stopped  |

| 001            | DIV1                | RTC clock / 1 (no prescaling) |

| 010            | DIV2                | RTC clock / 2                 |

| 011            | DIV8                | RTC clock / 8                 |

| 100            | DIV16               | RTC clock / 16                |

| 101            | DIV64               | RTC clock / 64                |

| 110            | DIV256              | RTC clock / 256               |

| 111            | DIV1024             | RTC clock / 1024              |

#### 18.3.2 STATUS – Status register

| Bit           | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0        |

|---------------|---|---|---|---|---|---|---|----------|

| +0x01         | - | - | - | - | - | - | - | SYNCBUSY |

| Read/Write    | R | R | R | R | R | R | R | R        |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0        |

#### • Bit 7:1 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always write these bits to zero when this register is written.

#### Bit 0 – SYNCBUSY: Synchronization Busy Flag

This flag is set when the CNT, CTRL, PER, or COMP register is busy synchronizing between the RTC clock and system clock domains after writing any of these registers or when waking up from a sleep mode where the peripheral clock is stopped. This flag is automatically cleared when the synchronisation is complete.

#### 18.3.3 INTCTRL – Interrupt Control register

| Bit           | 7 | 6 | 5 | 4 | 3      | 2         | 1      | 0        |

|---------------|---|---|---|---|--------|-----------|--------|----------|

| +0x02         | - | - | - | - | COMPIN | [LVL[1:0] | OVFINT | LVL[1:0] |

| Read/Write    | R | R | R | R | R/W    | R/W       | R/W    | R/W      |

| Initial Value | 0 | 0 | 0 | 0 | 0      | 0         | 0      | 0        |

#### • Bit 7:4 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always write these bits to zero when this register is written.

#### • Bit 3:2 – COMPINTLVL[1:0]: Compare Match Interrupt Enable

These bits enable the RTC compare match interrupt and select the interrupt level, as described in "Interrupts and Programmable Multilevel Interrupt Controller" on page 131. The enabled interrupt will trigger when COMPIF in the INTFLAGS register is set.

#### • Bit 1:0 – OVFINTLVL[1:0]: Overflow Interrupt Enable

These bits enable the RTC overflow interrupt and select the interrupt level, as described in "Interrupts and Programmable Multilevel Interrupt Controller" on page 131. The enabled interrupt will trigger when OVFIF in the INTFLAGS register is set.

#### 18.3.4 INTFLAGS - Interrupt Flag register

| Bit           | 7 | 6 | 5 | 4 | 3 | 2 | 1      | 0     |

|---------------|---|---|---|---|---|---|--------|-------|

| +0x03         | - | - | - | - | - | - | COMPIF | OVFIF |

| Read/Write    | R | R | R | R | R | R | R/W    | R/W   |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0 | 0      | 0     |

#### Bit 7:2 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always write these bits to zero when this register is written.

#### Bit 1 – COMPIF: Compare Match Interrupt Flag

This flag is set on the next count after a compare match condition occurs. It is cleared automatically when the RTC compare match interrupt vector is executed. The flag can also be cleared by writing a one to its bit location.

#### • Bit 0 – OVFIF: Overflow Interrupt Flag

This flag is set on the next count after an overflow condition occurs. It is cleared automatically when the RTC overflow interrupt vector is executed. The flag can also be cleared by writing a one to its bit location.

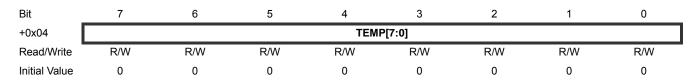

#### 18.3.5 TEMP – Temporary register

#### • Bit 7:0 – TEMP[7:0]: Temporary bits

This register is used for 16-bit access to the counter value, compare value, and TOP value registers. The low byte of the 16-bit register is stored here when it is written by the CPU. The high byte of the 16-bit register is stored when the low byte is read by the CPU. For more details, refer to "The combined EIND + Z register." on page 12.

#### 18.3.6 CNTL – Counter register Low

The CNTH and CNTL register pair represents the 16-bit value, CNT. CNT counts positive clock edges on the prescaled RTC clock. Reading and writing 16-bit values requires special attention. Refer to "The combined EIND + Z register." on page 12 for details.

Due to synchronization between the RTC clock and system clock domains, there is a latency of two RTC clock cycles from updating the register until this has an effect. Application software needs to check that the SYNCBUSY flag in the "STATUS – Status register" on page 214 is cleared before writing to this register or reading the register after waking up from a sleep mode where the peripheral clock is stopped

| Bit           | 7   | 6   | 5   | 4   | 3     | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-------|-----|-----|-----|

| +0x08         |     |     |     | CNT | [7:0] |     |     |     |

| Read/Write    | R/W | R/W | R/W | R/W | R/W   | R/W | R/W | R/W |

| Initial Value | 0   | 0   | 0   | 0   | 0     | 0   | 0   | 0   |

#### Bit 7:0 — CNT[7:0]: Counter Value low byte

These bits hold the LSB of the 16-bit real-time counter value.

#### 18.3.7 CNTH – Counter register High

| Bit           | 7   | 6   | 5   | 4    | 3     | 2   | 1   | 0   |

|---------------|-----|-----|-----|------|-------|-----|-----|-----|

| +0x09         |     |     |     | CNT[ | 15:8] |     |     |     |

| Read/Write    | R/W | R/W | R/W | R/W  | R/W   | R/W | R/W | R/W |

| Initial Value | 0   | 0   | 0   | 0    | 0     | 0   | 0   | 0   |

#### • Bit 7:0 – CNT[15:8]: Counter Value highbyte

These bits hold the MSB of the 16-bit real-time counter value.

#### 18.3.8 PERL – Period register Low

The PERH and PERL register pair represents the 16-bit value, PER. PER is constantly compared with the counter value (CNT). A match will set OVFIF in the INTFLAGS register and clear CNT. Reading and writing 16-bit values requires special attention. Refer to "The combined EIND + Z register." on page 12 for details.

Due to synchronization between the RTC clock and system clock domains, there is a latency of two RTC clock cycles from updating the register until this has an effect. Application software needs to check that the SYNCBUSY flag in the "STATUS – Status register" on page 214 is cleared before writing to this register.

| Bit           | 7   | 6   | 5   | 4   | 3     | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-------|-----|-----|-----|

| +0x0A         |     |     |     | PER | [7:0] |     |     |     |

| Read/Write    | R/W | R/W | R/W | R/W | R/W   | R/W | R/W | R/W |

| Initial Value | 1   | 1   | 1   | 1   | 1     | 1   | 1   | 1   |

#### Bit 7:0 – PER[7:0]: Period low byte

These bits hold the LSB of the 16-bit RTC TOP value.

#### 18.3.9 PERH – Period register High

| Bit           | 7   | 6   | 5   | 4    | 3     | 2   | 1   | 0   |

|---------------|-----|-----|-----|------|-------|-----|-----|-----|

| +0x0B         |     |     |     | PER[ | 15:8] |     |     |     |

| Read/Write    | R/W | R/W | R/W | R/W  | R/W   | R/W | R/W | R/W |

| Initial Value | 1   | 1   | 1   | 1    | 1     | 1   | 1   | 1   |

#### • Bits 7:0 – PER[15:8]: Period high byte

These bits hold the MSB of the 16-bit RTC TOP value.

#### 18.3.10 COMPL – Compare register Low

The COMPH and COMPL register pair represent the 16-bit value, COMP. COMP is constantly compared with the counter value (CNT). A compare match will set COMPIF in the INTFLAGS register. Reading and writing 16-bit values requires special attention. Refer "The combined EIND + Z register." on page 12 for details.

Due to synchronization between the RTC clock and system clock domains, there is a latency of two RTC clock cycles from updating the register until this has an effect. Application software needs to check that the SYNCBUSY flag in the "STATUS – Status register" on page 214 is cleared before writing to this register.

If the COMP value is higher than the PER value, no RTC compare match interrupt requests or events will ever be generated.

| Bit           | 7   | 6   | 5   | 4   | 3      | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|--------|-----|-----|-----|

| +0x0C         |     |     |     | COM | P[7:0] |     |     |     |

| Read/Write    | R/W | R/W | R/W | R/W | R/W    | R/W | R/W | R/W |

| Initial Value | 0   | 0   | 0   | 0   | 0      | 0   | 0   | 0   |

#### • Bit 7:0 – COMP[7:0]: Compare value low byte

These bits hold the LSB of the 16-bit RTC compare value.

#### 18.3.11 COMPH – Compare register High

| Bit           | 7   | 6   | 5   | 4    | 3       | 2   | 1   | 0   |

|---------------|-----|-----|-----|------|---------|-----|-----|-----|

| +0x0D         |     |     |     | COMF | 2[15:8] |     |     |     |

| Read/Write    | R/W | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Initial Value | 0   | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

#### • Bit 7:0 – COMP[15:8]: Compare value high byte

These bits hold the MSB of the 16-bit RTC compare value.

**Atmel**

# 18.4 Register summary

| Address | Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3    | Bit 2     | Bit 1       | Bit 0     | Page |

|---------|----------|-------|-------|-------|-------|----------|-----------|-------------|-----------|------|

| +0x00   | CTRL     | -     | _     | -     | -     | _        |           | PRESCALER[2 | 2:0]      | 214  |

| +0x01   | STATUS   | -     | -     | -     | -     | -        | -         | -           | SYNCBUSY  | 214  |

| +0x02   | INTCTRL  | -     | -     | -     | -     | COMPIN   | TLVL[1:0] | OVFIN       | TLVL[1:0] | 215  |

| +0x03   | INTFLAGS | -     | -     | -     | -     | -        | -         | COMPIF      | OVFIF     | 215  |

| +0x04   | TEMP     | -     | -     | -     | -     | -        | -         | COMPIF      | OVFIF     | 215  |

| +0x05   | Reserved | -     | -     | -     | -     | -        | -         | -           | -         |      |

| +0x06   | Reserved | -     | -     | -     | -     | -        | -         | -           | -         |      |

| +0x07   | Reserved | -     | -     | -     | -     | -        | -         | -           | -         |      |

| +0x08   | CNTL     |       |       |       | TEN   | /IP[7:0] |           |             |           | 216  |

| +0x09   | CNTH     |       |       |       | CN    | IT[7:0]  |           |             |           | 216  |

| +0x0A   | PERL     |       |       |       | CN    | T[15:8]  |           |             |           | 216  |

| +0x0B   | PERH     |       |       |       | PE    | R[7:0]   |           |             |           | 216  |

| +0x0C   | COMPL    |       |       |       | PEI   | R[15:8]  |           |             |           | 217  |

| +0x0D   | COMPH    |       |       |       | COI   | MP[7:0]  |           |             |           | 217  |

# 18.5 Interrupt Vector Summary

Table 18-2.

RTC interrupt vectors and their word offset.

| Offset | Source    | Interrupt description                            |

|--------|-----------|--------------------------------------------------|

| 0x00   | OVF_vect  | Real-time counter overflow interrupt vector      |

| 0x02   | COMP_vect | Real-time counter compare match interrupt vector |