NoC Power-Gating for Dark Silicon Era

As key building blocks of current and future computing systems, many-core chips are facing unprecedented power challenges — to the point where all on-chip components can no longer be powered “on” simultaneously so as to avoid overheating and damaging the chip. This leads to considerable portions of chips going dark, thus ushering in the era of dark silicon. To facilitate dark silicon computing, it is important for not only the computational resources (i.e., processor cores) but also the communication resources (i.e., on-chip networks, or NoCs) to be able to power “on” and “off” proportionally with computing load. Power-gating is one of the primary approaches to turn off NoC routers when possible.

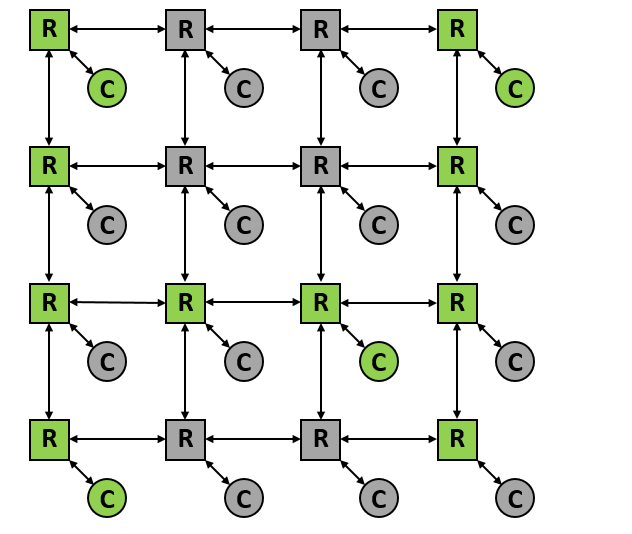

It is, however, much more difficult to achieve energy-proportional NoCs than energy-proportional cores. The difficulty comes from the fact that, even if only a few processing cores are active, the majority of the NoC routers may still need to be powered “on” to provide connected and deadlock-free paths that are needed to transport packets among the active cores (see the figure below). Moreover, the need to access shared cache and the existence of cache coherence traffic both demand additional connections even if processing cores are not active. Thus, innovative approaches and techniques are much needed to enable energy-proportional and performance scalable NoC designs in the dark silicon era.

|

Example: as shown in the figure, even with perfect routing, 4 active cores may require 10 out of the 16 routers to be powered "on" to provide connected paths. If using the common 2D mesh topology and XY routing, 15 out of the 16 routers are required to be powered "on"! Significant investigation on more efficient topology, routing, flow-control, router architecture, reconfigurable schemes, etc. is much needed to enable energy-proportional NoCs. |

The Agate Simulator

To facilitate further research advancement, we developed a cycle-accurate NoC power-gating simulation infrastructure named Agate. The Agate simulator is fully compatible with Gem5 for closed-loop, full-system simulation of NoC-based many-core computing systems.

This is a joint effort by three research groups: the STAR Lab at Oregon State University, the SMART Interconnects Group at the University of Southern California, and the SPORT Lab at the University of Southern California.

Download

- The Agate simulator is available for download here.

Update: Rashid Aligholipur at Isfahan University of Technology has adapted Agate to be working with Garnet 2.0 in Gem5. If you are interested in the source code, please send him an email.

Manual

- The latest version of Agate User's Guide is Agate_Manual_v1.2.pdf. We may update the manual in the future when needed.

Publication

- Lizhong Chen, Di Zhu, Massoud Pedram, and Timothy M. Pinkston, "Simulation of NoC Power-Gating: Requirements, Optimizations, and the Agate Simulator", in Journal of Parallel and Distributed Computing (JPDC), 95 (2016): 69-78.

People

- Lizhong Chen

- Di Zhu

- Massoud Pedram

- Timothy Pinkston

Acknowledgment

- This work is supported, in part, by the National Science Foundation (NSF) grants CCF-1619456 and CCF-1321131.

A Brief Reference Guide

To help more researchers get started with projects in NoC power-gating, below is a brief guide on related papers.

Coarse-grained Router Power-Gating

Many of the recent works focus on powering "on" and "off" on-chip networks at per-router granularity. The following papers are highly recommended for reading to understand the challenges, opportunities and potential solutions for NoC power-gating.

- NoRD: Node-Router Decoupling for Effective Power-gating of On-Chip Routers

L. Chen and T. M. Pinkston, MICRO 2012 - Energy-efficient Interconnect via Router Parking

A. Samih, W. Ren, A. Krishna, C. Maciocco, C. Tai, and Y. Solihin, HPCA 2013 - Catnap: Energy Proportional Multiple Network-on-Chip

R. Das, S. Narayanasamy, S. K. Satpathy, and R. G. Dreslinski, ISCA 2013 - MP3: Minimizing Performance Penalty for Power-gating of Clos Network-on-Chip

L. Chen, L. Zhao, R. Wang, and T. M. Pinkston, HPCA 2014 - Power Punch: Towards Non-blocking Power-gating of NoC Routers

L. Chen, D. Zhu, M. Pedram, and T. M. Pinkston, HPCA 2015

Fine-grained Router Power-Gating

Some earlier works power-gate various components within a router, such as per port or per virtual channel.

- Run-time Power Gating of On-chip Routers Using Look-ahead Routing

H. Matsutani, M. Koibuchi, W. Daihan, and H. Amano, ASP-DAC 2008 - Adding Slow-silent Virtual Channels For Low-power On-chip Networks

H. Matsutani, M. Koibuchi, D. Wang, and H. Amano, NOCS 2008 - Ultra Fine-grained Run-time Power Gating of On-chip Routers for CMPs

H. Matsutani, M. Koibuchi, D. Ikebuchi, K. Usami, H. Nakamura, and H. Amano, NOCS 2010

NoC Power-Gating with Some Software Support

- Smart Butterfly: Reducing Static Power Dissipation of Network-on-Chip with Core-State-Awareness

S. Yue, L. Chen, D. Zhu, T. M. Pinkston, and M. Pedram, ISLPED 2014 - NoC-Sprinting: Interconnect for Fine-grained Sprinting in the Dark Silicon Era

J. Zhan, Y. Xie, and G. Sun, DAC 2014 - Power-aware NoCs through Routing and Topology Reconfiguration

R. Parikh, R. Das, and V. Bertacco, DAC 2014 - DimNoC: A Dim Silicon Approach Towards Power-efficient On-chip Network

J. Zhan, J. Ouyang, F. Ge, J. Zhao, and Y. Xie, DAC 2015

Some Other Important Related Papers

To be added soon. Meanwhile, if you have publications that make significant contribution to NoC power-gating, please let me know and I would be happy to add them to this list.