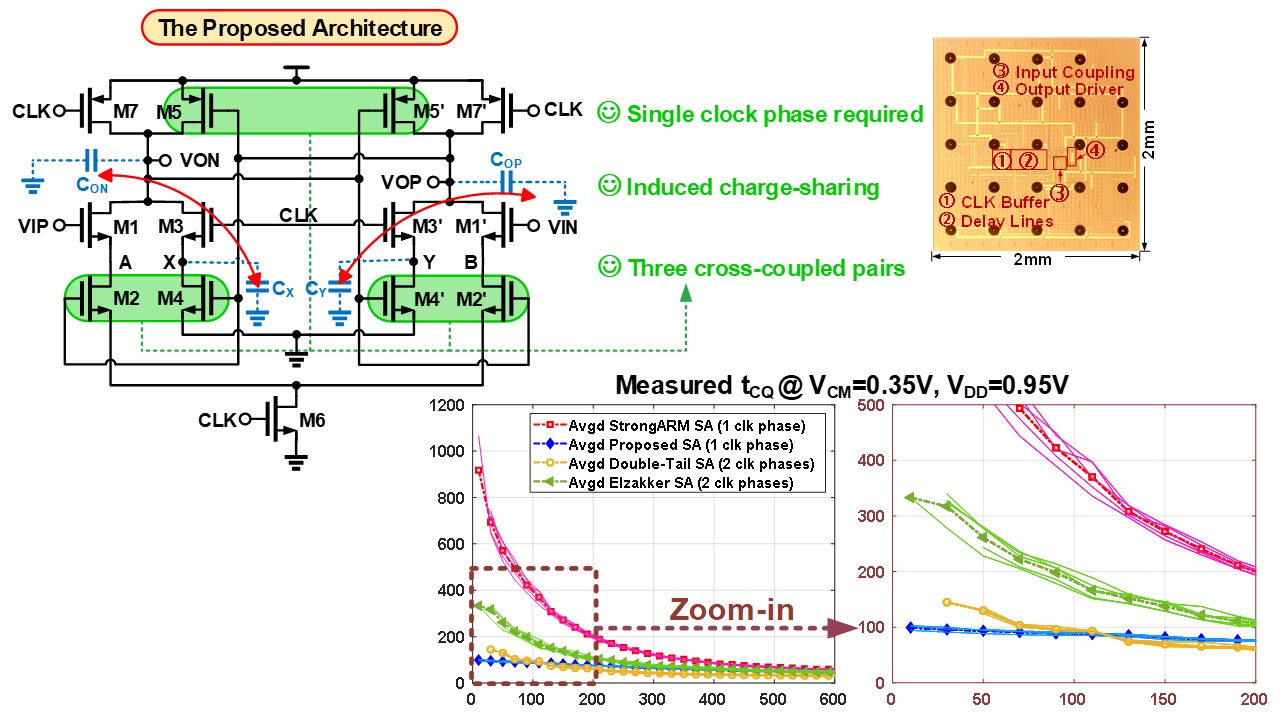

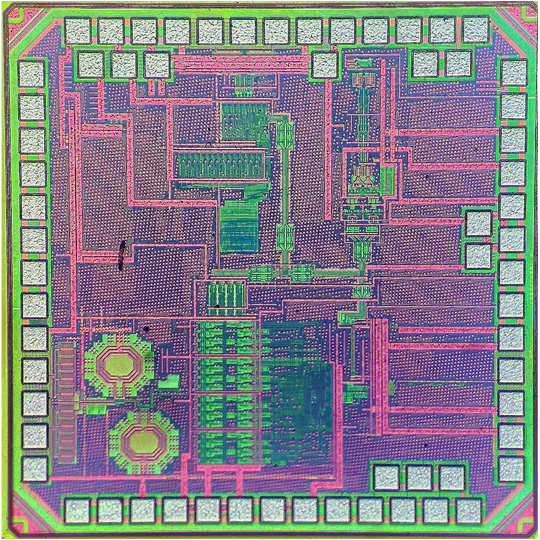

(VLSI 2022) A Sense Amplifier Architecture

A single-clock-phase sense amplifier architecture with 9x smaller clock-to-Q delay compared to the StrongARM architecture & 6.3dB lower noise compared to Double-Tail architecture in 22nm FinFET.

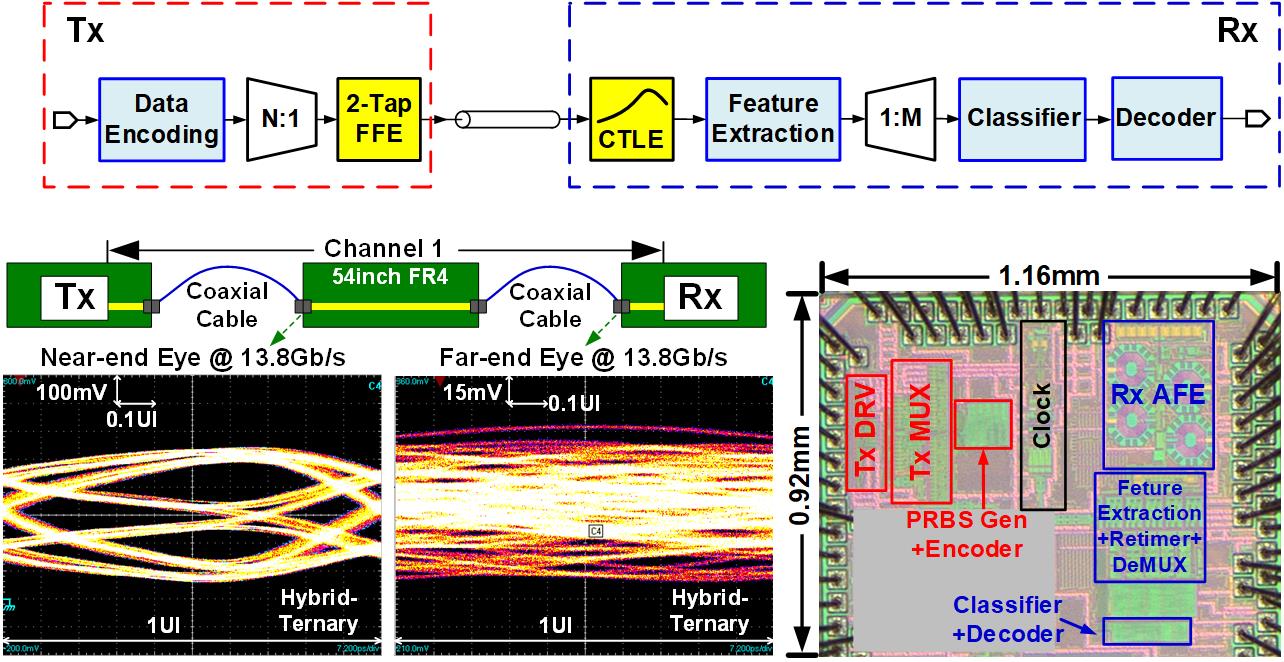

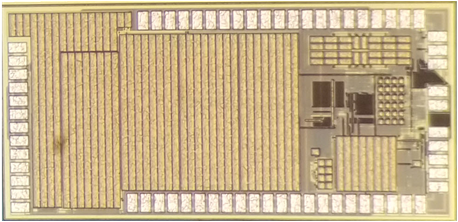

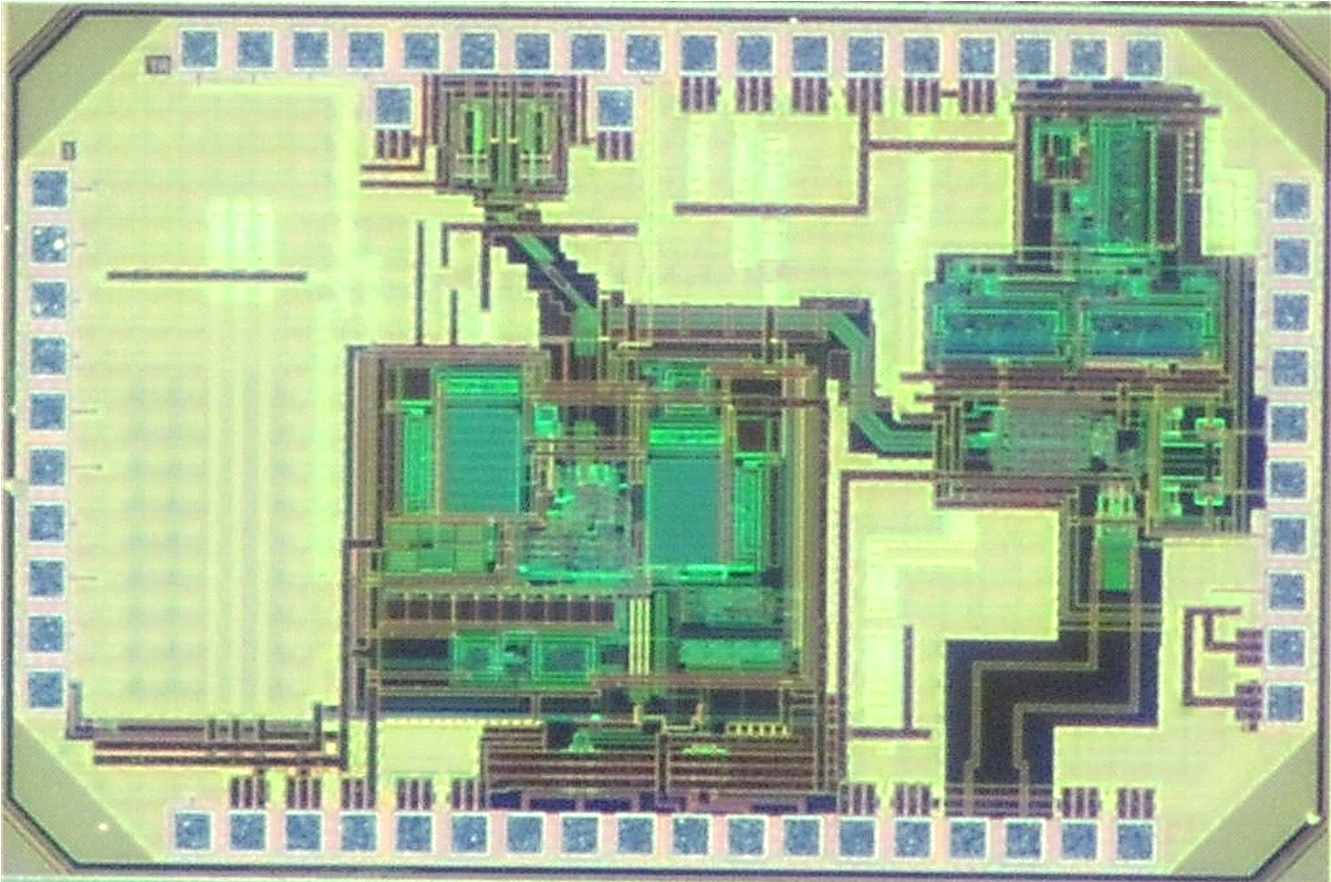

(VLSI 2021) A Machine Learning Inspired Wireline Transceiver

The transceiver uses machine learning principles such as feature extraction and classification to communicate on a 40dB+ channel loss. It can achieve communication on a 44.7dB loss FR4 channel with BER less than 1×10-6, and an energy efficiency of 7.3pJ/bit at 13.8Gb/s in 65nm CMOS.

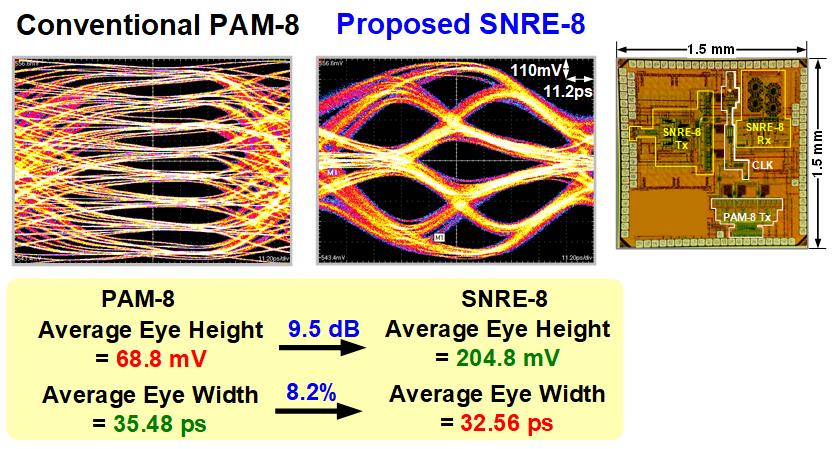

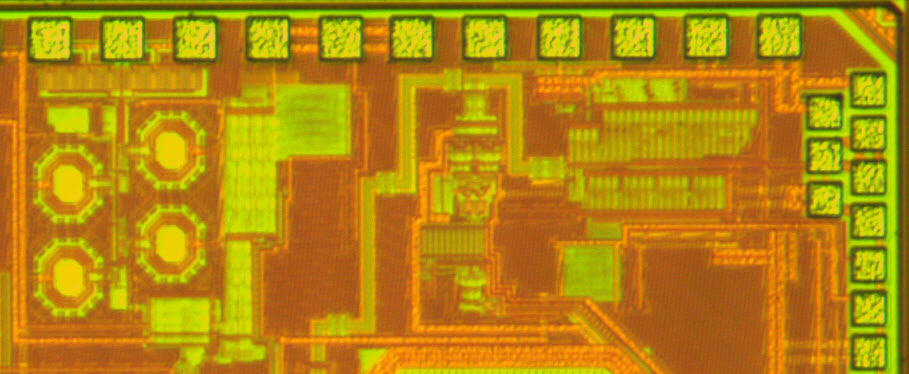

(VLSI 2021) SNR Enhanced Modulation (SNRE-8) for Wireline Transceivers

The proposed modulation (SNR-Enhanced), modulates the pulse width and amplitude to achieve an average SNR improvement of 9.5 dB over PAM-8. The 27Gb/s transceiver achieves 1×10-7 BER at 9 dB channel loss with an efficiency of 5.39 pJ/bit in the 65 nm CMOS process.

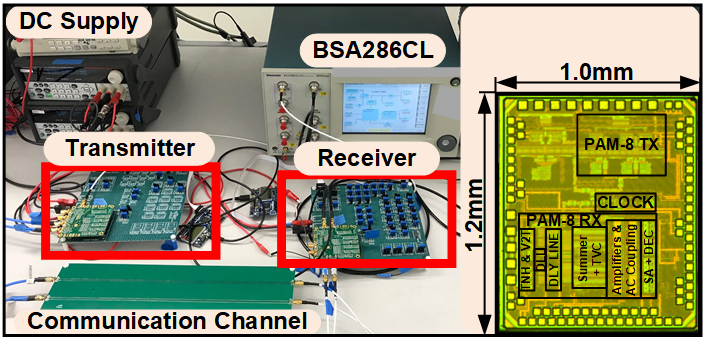

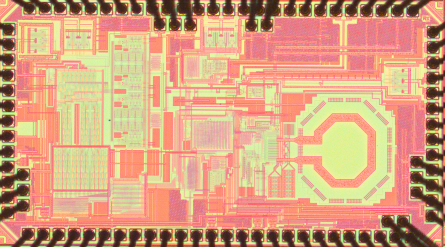

(ESSCIRC 2019) A 39.6 Gb/s PAM-8 Wireline Transceiver

The PAM-8 wireline trasnceiver uses front-end time domain signal processing and performs non-linearity cancellation. The proposed transceiver can operate from 12.0 Gb/s to 39.6 Gb/s and compensates 14 dB loss at 6.6 GHz with an efficiency of 8.66pJ/bit in 65nm CMOS.

(CICC 2019) Equalizer Free Communication For Bandwidth Limited Channels

We present an alternative strategy for communicating on bandwidth limited wireline channels *without* using conventional equalizers (FFE, DFE, CTLE): Dicode encoding, ISI error correction and decoding. Compared to the state-of-the-art Viterbi-based transceivers, the proposed transceiver achieves 4x better energy efficiency, 3x higher data rate, and 30x lower latency.

(CICC 2019) Source + Switched Capacitor Harvester with No Top and Bottom Plate Switching Loss

We present a new switching technique, which helps to break the trade-off between switching loss and charge redistribution loss in a switched capacitor. The proposed switching avoids charging and discharging of top and bottom plate parasitic capacitors. As a result, the energy lost in switching the top and bottom plate parasitic capacitors is zero joules.

(ISSCC 2018) Clock Domain Equalization using iPWM Encoding for Low Voltage Wireline Links

Low voltage transceiver equalization is a challenge. We propose clock domain equalization (signal processing) based wireline transceiver architecture. In the proposed transceiver, equalization is performed in the subrate clock at very-low bandwidth, which helps to equalize heavy channel loss even at 0.5V supply. Our transceiver operates from 0.5-to-0.9V (3-to-16Gb/s) and equalize 27dB Loss at 10Gb/s (1.8pJ/bit).

(ISSCC 2017) A New Line-Coding Scheme for Energy Efficient Equalization - Integrated Pulse Width Modulation (iPWM)

We invented a new line-coding scheme to efficiently equalize lossy wireline channels. The proposed encoding scheme is demonstrated on a 10-18Gb/s wireline transceiver using 65nm CMOS. Operating at 16Gb/s, the complete transceiver achieves an energy efficiency of 4.37pJ/bit and can equalize 27dB channel loss.

(ISSCC 2017, JSSC 2015) A 7Gb/s Embedded Clock Transceiver for Energy Proportional Links

We developed architecture and circuit techniques to achieve rapid-on/off in PLL, transmitter and receiver. The proposed transceiver demonstrates power scalability and energy proportional operation with a wide range of link utilization. This transceiver can power-on and lock in less than 20ns.

(ISSCC 2013, JSSC 2014) A 5Gb/s, 10ns Power-On-Time, 36μW Off-State Power, Fast Power-On Transmitter for Energy Proportional Links

We developed the transmitter with digital regulators and MDLL based clock to achieve rapid-on/off oepration. By using highly digital architecture the 2.5GHz MDLL achieves power-on-lock in 10ns (3 reference cycles).

(VLSI 2015, JSSC 2016) A VCO Based Highly Digital Temperature Sensor with 0.034oC/mV Supply Sensitivity

We developed a self-referenced VCO-based temperature sensor with reduced supply sensitivity in 65nm CMOS. A novel sensing technique is proposed in which temperature information is acquired by evaluating the ratio of the output frequencies of two ring oscillators.

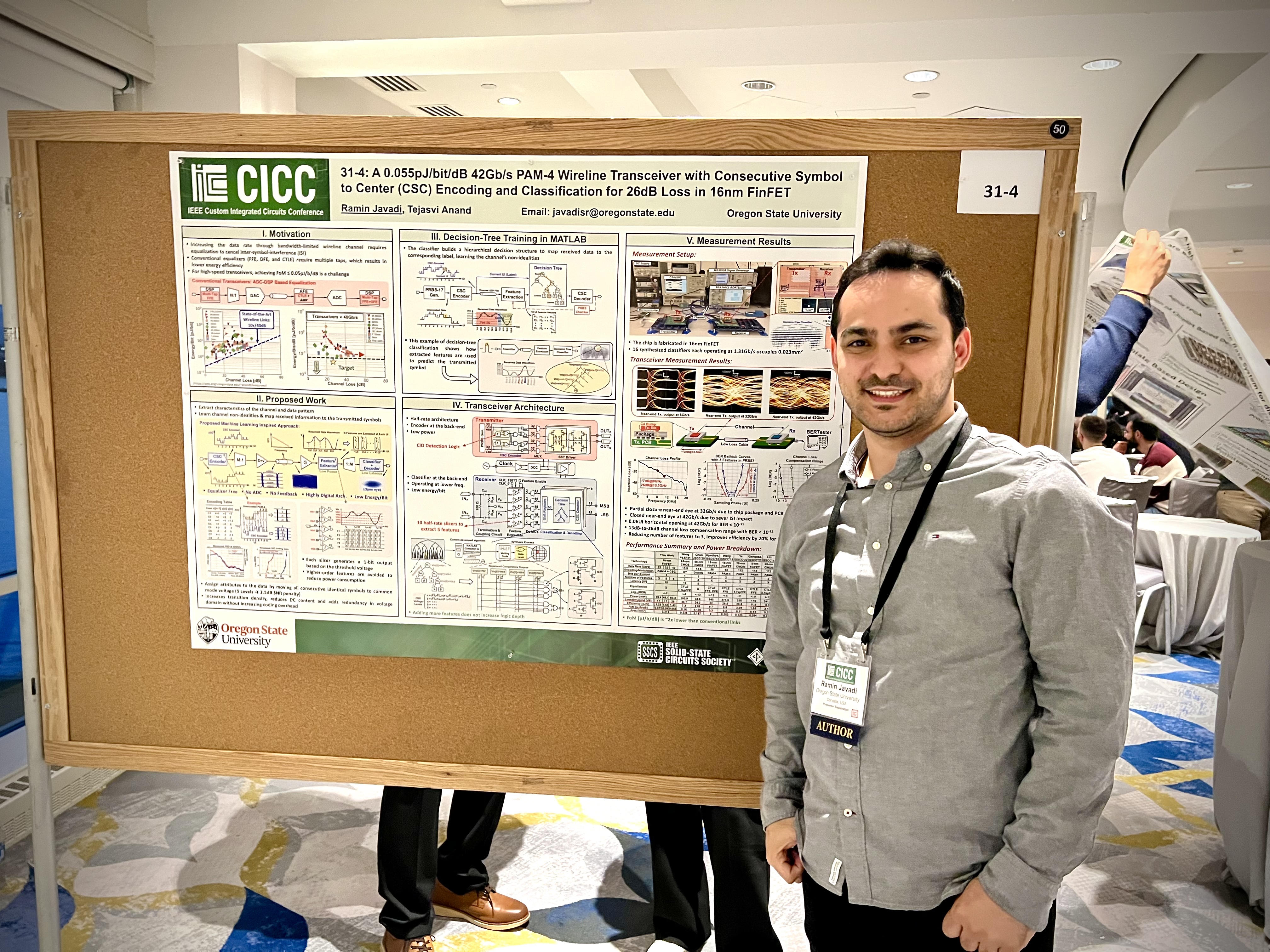

November 2025: Ramin Javadi won the prestigious Analog Devices Outstanding Student Designer Award. Congratulations Ramin!

November 2025: Ramin Javadi won the prestigious Analog Devices Outstanding Student Designer Award. Congratulations Ramin!